# Design and Implementation of a Linear Optical Receiver

#### Sara Radfar

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of

Master of Applied Science (Electrical Engineering) at

Concordia University

Montréal, Québec, Canada

**July 2025**

© Sara Radfar, 2025

## CONCORDIA UNIVERSITY

## School of Graduate Studies

| This is to certify t | that the thesis | prepared |

|----------------------|-----------------|----------|

|----------------------|-----------------|----------|

Sara Radfar

By:

| Entitled:          | Design and Implem                          | nentation of a Linear Optical                         | Receiver                    |

|--------------------|--------------------------------------------|-------------------------------------------------------|-----------------------------|

| and submitted in   | partial fulfillment of the                 | e requirements for the degree of                      | ,                           |

|                    | Master of Applied                          | d Science (Electrical Engineer                        | ring)                       |

| complies with th   | e regulations of this Un                   | niversity and meets the accepted                      | d standards with respect to |

| originality and qu | ıality.                                    |                                                       |                             |

| Signed by the Fir  | nal Examining Committe                     | ee:                                                   |                             |

|                    | Dr. Rabin Raut                             |                                                       | _ Chair                     |

|                    | Dr. Brandon Helfield                       | 1                                                     | _ External Examiner         |

|                    | Dr. Rabin Raut                             |                                                       | _ Examiner                  |

|                    | Dr. Glenn Cowan                            |                                                       | _ Supervisor                |

| Approved by        | Dr. Abdelwahab Har<br>Department of Electr | mou-Lhadj, Chair<br>rical and Computer Engineering    | 9                           |

|                    | 2025                                       | Dr. Mourad Debbabi, Dean Faculty of Engineering and C | Computer Science            |

## **Abstract**

#### Design and Implementation of a Linear Optical Receiver

#### Sara Radfar

Rising internet traffic from AI and bandwidth-intensive applications has increased the demand for fast, low-power optical links in modern data centers. Multi-level modulation schemes such as four-level pulse amplitude modulation (PAM-4) improve spectral efficiency and throughput while relaxing bandwidth requirements. However, PAM-4 imposes strict linearity demands on the optical receiver's analog front-end, particularly the main amplifier.

This thesis presents a highly linear, power-efficient main amplifier for PAM-4 and NRZ optical receivers, implemented in 65-nm CMOS. The design uses a  $g_m/g_m$  topology with interleaved active feedback (IAFB) to extend bandwidth without passive inductors. Linearity is further improved by reducing third-order distortion through resistive voltage dividers at the feedback inverters' inputs and by increasing their gain. Post-layout simulations show superior bandwidth, linearity, and vertical eye opening (VEO) compared to a conventional Cherry–Hooper amplifier, including a 67% reduction in total harmonic distortion (THD) at a 500-m $V_{pp}$  output swing.

To mitigate channel impairments, equalization is integrated directly into the main amplifier by introducing a pole within the active feedback loop. This removes the need for a separate continuous-time linear equalizer (CTLE), reducing chip area and power. The proposed amplifier is part of a four-channel differential optical receiver, fabricated with a total chip area of 2 mm × 1 mm. Post-layout results indicate 10-Gb/s per-channel operation for both NRZ and PAM-4, with about 30 mW power consumption per channel.

# Acknowledgments

I would like to express my sincere gratitude to my supervisor, Prof. Glenn Cowan, for his invaluable guidance throughout this program. I have gained significant knowledge from his expertise and passion for analog and mixed-signal IC design, and I am truly grateful for the opportunity to be part of his enthusiastic team at Concordia University.

I would also like to thank the Canadian Microelectronics Corporation (CMC) for their support and assistance throughout this project. My sincere thanks go as well to Dr. David Rolston for his valuable contributions to the development of this work.

I am deeply grateful to all members of our research group, especially my friend and office-mate Ata Mahsafar, for the many insightful discussions and his generous help throughout this journey. I also thank Di Zhang, Abdullah Ibn Abbas, and Vinicius Sirtoli for sharing their knowledge and support along the way.

Words cannot fully convey my gratitude to my beloved family, whose love and support have carried me through this journey. To my mother, who has always been my greatest source of encouragement and has inspired me to pursue ambitious goals. To my father, whom I lost during this program. Thank you for always believing in me; your presence is deeply missed. And to my sister, Marjan, a constant source of support; thank you for setting the bar so high and showing me what is possible.

Lastly, I would like to thank my husband, Amin, with all my heart. We began this journey together, and I could not have made it through without his unwavering support. He has always been by my side, seeing the best in me and reminding me of my capabilities when I needed it most.

# **Contents**

| Li             | List of Figures List of Tables |                                                        | viii |

|----------------|--------------------------------|--------------------------------------------------------|------|

| Li             |                                |                                                        | xiii |

| 1 Introduction |                                | duction                                                | 1    |

|                | 1.1                            | Motivation                                             | 2    |

|                | 1.2                            | Publications and Contributions of the Author           | 3    |

|                | 1.3                            | Thesis Organization                                    | 3    |

| 2              | Bac                            | ground and Literature Review                           | 5    |

|                | 2.1                            | Modulation Formats                                     | 6    |

|                | 2.2                            | Eye Diagram                                            | 6    |

|                | 2.3                            | Linearity Metrics in Optical Transceivers              | 8    |

|                |                                | 2.3.1 Total Harmonic Distortion (THD)                  | 8    |

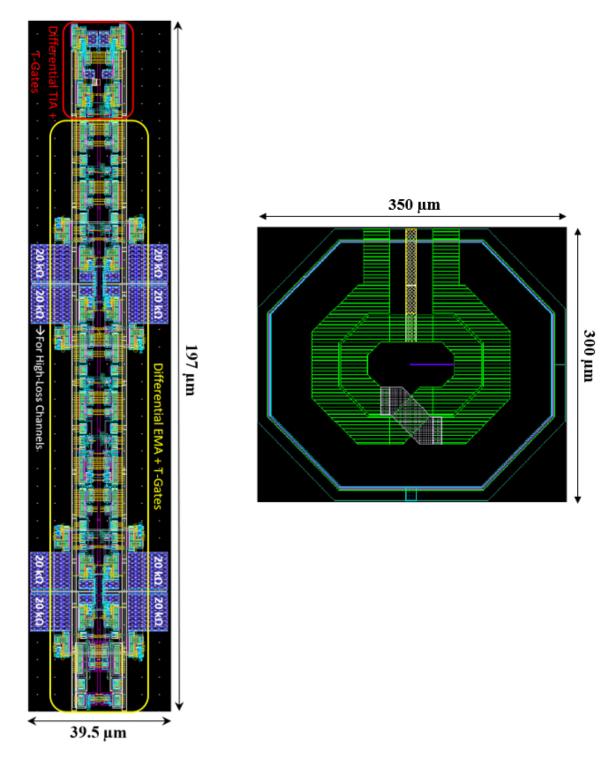

|                |                                | 2.3.2 Ratio Level Mismatch (RLM)                       | 9    |

|                | 2.4                            | Inverter-based Main Amplifiers                         | 11   |

|                |                                | 2.4.1 Cherry-Hooper (CH) Amplifier                     | 11   |

|                |                                | 2.4.2 $g_m/g_m$ Amplifier                              | 12   |

|                | 2.5                            | Inductorless Bandwidth Extension Techniques            | 17   |

|                |                                | 2.5.1 Interleaving Active Feedback (IAFB)              | 17   |

|                | 2.6                            | Equalizing the Electrical Channel in Optical Receivers | 23   |

|                |                                | 2.6.1 Equalizing Main Amplifier (EMA)                  | 25   |

|   | 2.7   | Conclu    | asion                                                                    | 28 |

|---|-------|-----------|--------------------------------------------------------------------------|----|

| 3 | Line  | ear Mai   | n Amplifier                                                              | 29 |

|   | 3.1   | $g_m/g_m$ | <sub>n</sub> -based Main Amplifier Design                                | 29 |

|   |       | 3.1.1     | Bandwidth Extension Technique                                            | 29 |

|   | 3.2   | Design    | Methodology and Simulation Results                                       | 30 |

|   |       | 3.2.1     | PMOS to NMOS Ratio                                                       | 30 |

|   |       | 3.2.2     | Gain Selection                                                           | 31 |

|   | 3.3   | Linear    | ity Improvement                                                          | 36 |

|   |       | 3.3.1     | Effect of Third Nonlinear Coefficients on THD                            | 37 |

|   |       | 3.3.2     | Resistive Voltage Division in Feedback Loops                             | 38 |

|   |       | 3.3.3     | Design Methodology and Simulation Results                                | 39 |

|   | 3.4   | Conclu    | asion                                                                    | 43 |

| 4 | Equ   | alizing   | Main Amplifier                                                           | 45 |

|   | 4.1   | Impact    | t of Channel Losses                                                      | 45 |

|   | 4.2   | Equali    | zing MA Based on a Third-Order Gain Stage                                | 47 |

|   | 4.3   | Conclu    | asion                                                                    | 54 |

| 5 | Desi  | gn and    | Implementation of a Differential Linear Optical Receiver with an Equaliz | -  |

|   | ing l | Main A    | mplifier                                                                 | 55 |

|   | 5.1   | Fully I   | Differential Design                                                      | 55 |

|   |       | 5.1.1     | Cross-Coupled Inverters                                                  | 56 |

|   |       | 5.1.2     | Differential Photodiodes                                                 | 57 |

|   | 5.2   | 4-Chai    | nnel Linear Optical Receiver Chip Design                                 | 58 |

|   |       | 5.2.1     | Layout Design                                                            | 59 |

|   |       | 5.2.2     | Post-layout Simulation Results                                           | 61 |

|   |       | 5.2.3     | Chip Floorplan of the 4-Channel Optical Receiver                         | 64 |

|   |       | 5.2.4     | Fabricated Chip in 65 nm CMOS Technology                                 | 66 |

|   | 5 3   | Conclu    | ucion                                                                    | 6  |

| 6   | Com    | parison and Conclusion                      | 68 |

|-----|--------|---------------------------------------------|----|

|     | 6.1    | Comparison of the Proposed Optical Receiver | 68 |

|     | 6.2    | Conclusion                                  | 69 |

|     | 6.3    | Future Works                                | 71 |

| Ap  | pendi  | ix A High-speed PCB Design                  | 73 |

| Bil | bliogr | aphy                                        | 75 |

# **List of Figures**

| Figure 2.1  | Block diagram of a typical short-reach optical link [9]                        | 5  |

|-------------|--------------------------------------------------------------------------------|----|

| Figure 2.2  | Time-domain representations of signals used to encode binary data include:     |    |

| (a) an      | example of an NRZ (PAM-2), (b) an example of a PAM-4 signal, (c) the eye       |    |

| diagra      | am corresponding to PAM-2, and (d) the eye diagram for PAM-4 [10]              | 6  |

| Figure 2.3  | Formation of an eye diagram by dividing the signal into segments of two unit   |    |

| interv      | als long: (a) NRZ signal; (b) resulting eye diagram, indicating minimal inter- |    |

| symbo       | ol interference (ISI); (c) NRZ signal; (d) corresponding eye diagram, showing  |    |

| notice      | able ISI effects [10]                                                          | 7  |

| Figure 2.4  | Signal level definitions for ratio level mismatch [10]                         | 10 |

| Figure 2.5  | Inverter-based Cherry-Hooper amplifier                                         | 11 |

| Figure 2.6  | Schematic diagram of (a) a transconductor, and (b) diode-connected inverter.   | 13 |

| Figure 2.7  | Block diagram of the $g_m/g_m$ amplifier                                       | 14 |

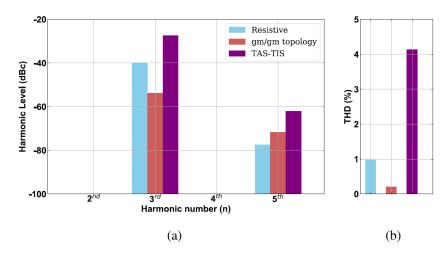

| Figure 2.8  | Comparison of different amplifier topologies. (a) Resistive load amplifier.    |    |

| (b) $g_m$   | $g_m$ amplifier. (c) TAS-TIS (Cherry-Hooper) amplifier [5]                     | 14 |

| Figure 2.9  | Linearity comparison of different amplifier topologies: (a) Harmonic levels,   |    |

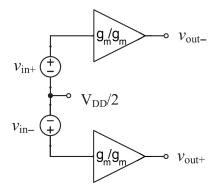

| (b) TH      | HD [5]                                                                         | 15 |

| Figure 2.10 | $g_m/g_m$ amplifiers in a pseudo-differential structure                        | 15 |

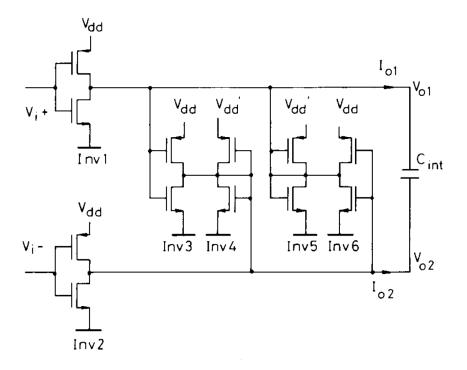

| Figure 2.11 | Linear transconductance structure proposed in [15]                             | 16 |

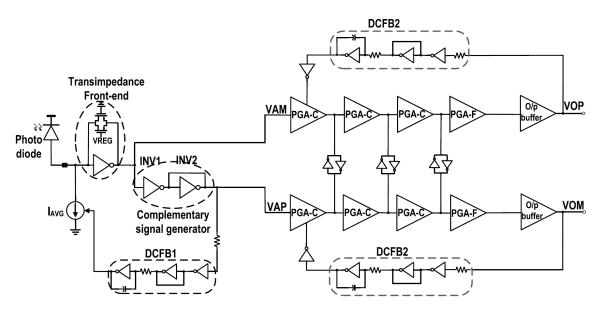

| Figure 2.12 | Schematic of the proposed linear optical receiver in [5]                       | 17 |

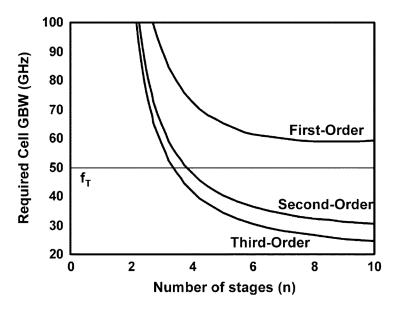

| Figure 2.13 | The relationship between the GBW product and the number of stages for          |    |

| $A_{tot} =$ | = $40\mathrm{dB}$ and $BW_{\mathrm{tot}}=10\mathrm{GHz}$ [8]                   | 18 |

| Figure 2.14 (a) Block diagram and (b) circuit schematic of conventional third-order gain         |    |

|--------------------------------------------------------------------------------------------------|----|

| stages with active feedback [8]                                                                  | 20 |

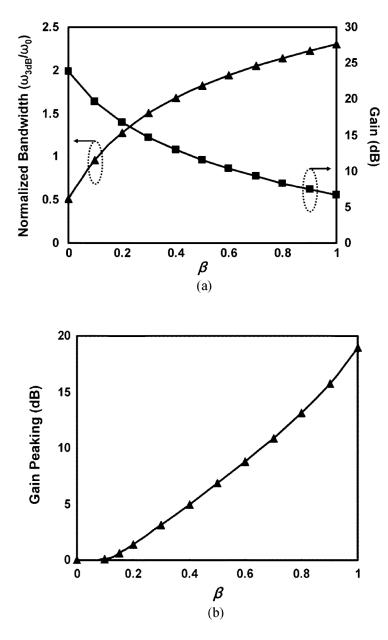

| Figure 2.15 Variations of (a) gain and normalized bandwidth, and (b) gain peaking of the         |    |

| conventional third-order amplifier by increasing the feedback gain $\beta$ [8]                   | 21 |

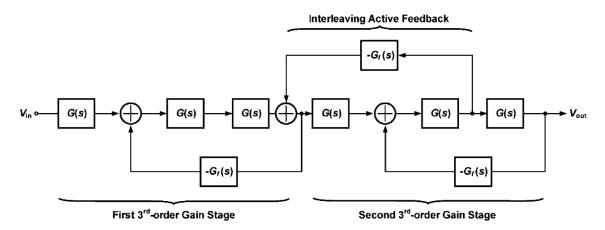

| Figure 2.16 Block diagram of the cascaded third-order stages with the proposed inter-            |    |

| leaving feedback in [8]                                                                          | 22 |

| Figure 2.17 Pole splitting behavior of the proposed feedback technique in [8]                    | 23 |

| Figure 2.18 (a) Simulated frequency response of the cascaded architecture with nonuni-           |    |

| form third-order gain stages; (b) Simulated frequency response of the cascaded                   |    |

| third-order gain stages [8]                                                                      | 23 |

| Figure 2.19 Block diagram of an optical receiver link: (a) employing a CTLE stage for            |    |

| equalization, and (b) utilizing an equalizing main amplifier to compensate for chan-             |    |

| nel losses                                                                                       | 24 |

| Figure 2.20 Equalization as channel inversion: (a) frequency response of the channel; (b)        |    |

| frequency response of an equalizer; (c) overall frequency response [10]                          | 25 |

| Figure 2.21 Block diagram of (a) the third-order EMA in [27] with a LPF inserted in              |    |

| each feedback path (b) amplitude response of the EMA for various ratios of $\omega_Z/\omega_1$ . | 27 |

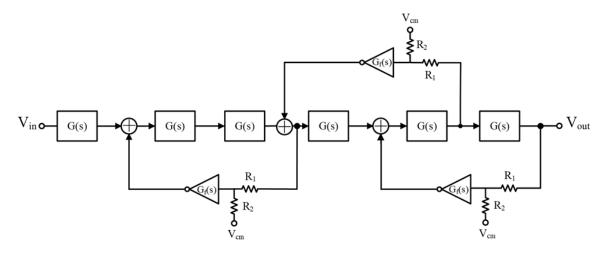

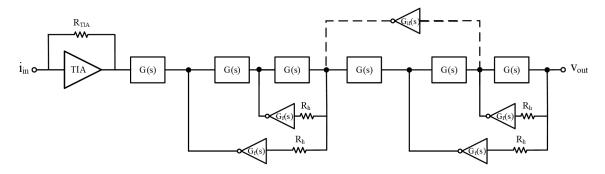

| Figure 3.1 Block diagram of the proposed PAM-4 linear main amplifier using $g_m/g_m$ -           |    |

| based amplifiers and IAFB technique                                                              | 30 |

| Figure 3.2 Gain peaking for different combinations of $G(0)$ and $G_f(0)$ to have a total        |    |

| gain of 64                                                                                       | 32 |

| Figure 3.3 Pole location variations of the proposed design for different combinations            |    |

| of $G(s)$ and $G_f(s)$ to have a total gain of 64. The red markers represent the pole            |    |

| locations of the design with $G(0)$ =3 and $G_f(0)$ =0.23                                        | 32 |

| Figure 3.4 VEO variations of the six-stage $g_m/g_m$ design with IAFB in different com-          |    |

| binations of $G(0)$ and $G_f(0)$                                                                 | 33 |

| Figure 3.5 Frequency response of the six-stage $g_m/g_m$ -based design with and without          |    |

| IAFB at $G(0)=3$ and $G_f(0)=0.23$ , and six-stage CH-based amplifier                            | 33 |

| Figure 3.6  | THD of the six-stage $g_m/g_m$ -based design with and without IAFB at $G(0)$ =3      |    |

|-------------|--------------------------------------------------------------------------------------|----|

| and $G$     | f(0)=0.23, and six-stage CH-based main amplifier                                     | 34 |

| Figure 3.7  | Schematic of the shunt-feedback TIA used in the optical receiver                     | 35 |

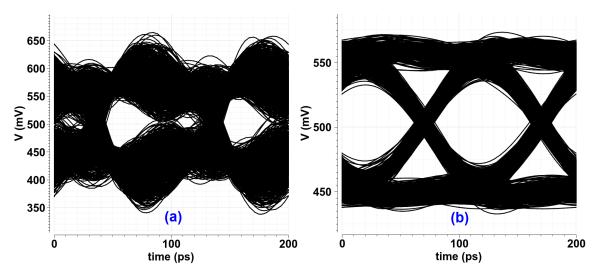

| Figure 3.8  | The eye diagrams of the proposed design in a) NRZ, b) PAM-4 at $G(0)$ =3             |    |

| and $G$     | $f_f(0)$ =0.23 with 40 ps of UI                                                      | 35 |

| Figure 3.9  | The eye diagrams of the CH-based design in a) NRZ, b) PAM-4 with 40 ps               |    |

| of UI.      |                                                                                      | 36 |

| Figure 3.10 | Block diagram of a third-order amplifier with feedback                               | 37 |

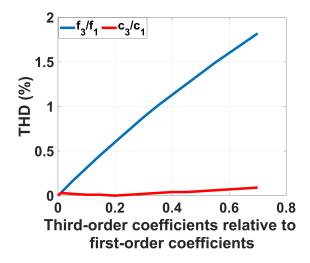

| Figure 3.11 | THD variations when increasing the third nonlinear coefficients                      | 38 |

| Figure 3.12 | Block diagram of the proposed PAM-4 linear main amplifier using $g_m/g_m$ -          |    |

| based       | amplifiers and IAFB technique with resistive voltage dividers                        | 39 |

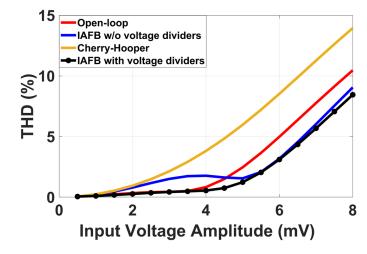

| Figure 3.13 | THD variations of different structures when increasing the input voltage am-         |    |

| plitud      | e                                                                                    | 4( |

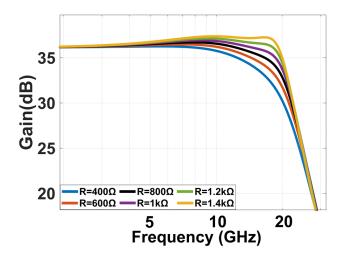

| Figure 3.14 | HFP and bandwidth variations of the proposed design when increasing the              |    |

| resisto     | or values.                                                                           | 41 |

| Figure 3.15 | Frequency responses of all four structures                                           | 41 |

| Figure 3.16 | The eye diagrams of the proposed design with enhanced linearity in a) NRZ,           |    |

| and b)      | PAM-4 with 40 ps of UI.                                                              | 42 |

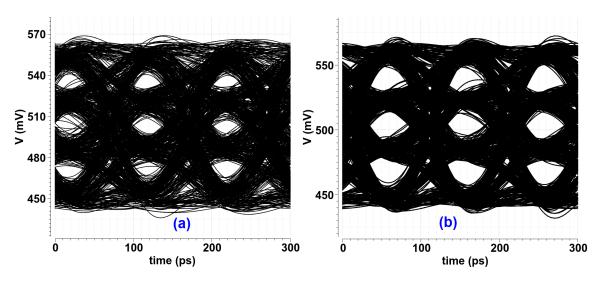

| Figure 4.1  | a) NRZ, and b) PAM-4 eye diagram of the proposed linear optical receiver             |    |

| in Cha      | apter 3 at 10 and 20 Gb/s, respectively, when simulated with a measured PCB          |    |

| trace o     | channel model                                                                        | 46 |

| Figure 4.2  | NRZ eye diagram of the proposed linear optical receiver in Chapter 3 at              |    |

| 10 Gb       | /s in differential structure when a) driving a 50 $\Omega$ load, b) simulated with a |    |

| high-l      | oss channel modeled as a 4-port differential system [30]                             | 46 |

| Figure 4.3  | Equalizing third-order gain stage                                                    | 47 |

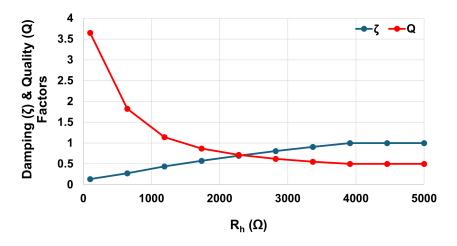

| Figure 4.4  | Variations of the third-order gain cell's conjugate poles' quality and damping       |    |

| factors     | s when decreasing the zero frequency or increasing $R_h$                             | 49 |

| Figure 4.5  | High-frequency peaking of the third-order equalizing amplifier when in-              |    |

| crassi      | ng nole O from 0.1 to 1.9                                                            | 50 |

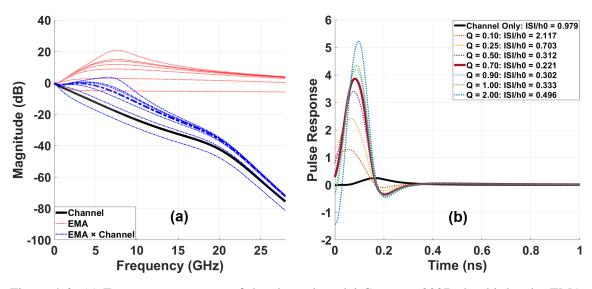

| Figure 4.6  | (a) Frequency responses of the channel model Carusone:2007, the third-            |    |

|-------------|-----------------------------------------------------------------------------------|----|

| order       | EMA, and their cascade for different pole-Q values; (b) Pulse responses of        |    |

| the ca      | scaded channel and third-order EMA for various pole Q values                      | 50 |

| Figure 4.7  | Proposed linear optical receiver with equalizing main amplifier                   | 51 |

| Figure 4.8  | NRZ eye diagram of the proposed equalizing main amplifier at 10 Gb/s data         |    |

| rate (a     | a) at the input of the measured channel and (b) at the output of the measured     |    |

| chann       | el                                                                                | 52 |

| Figure 4.9  | PAM-4 eye diagram of the proposed equalizing main amplifier at a 20 Gb/s          |    |

| data r      | rate using (a) the measured PCB trace channel model and (b) a 25% shorter         |    |

| versio      | on of the same channel model                                                      | 52 |

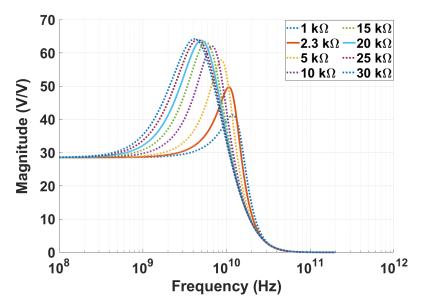

| Figure 4.10 | Frequency response of the proposed EMA when increasing $R_h$                      | 53 |

| Figure 4.11 | NRZ eye diagram of the proposed EMA at 10 Gb/s in differential structure          |    |

| when        | a) driving a 50 $\Omega$ load, b) simulated with a high-loss channel modeled as a |    |

| 4-por       | t differential system [30]                                                        | 54 |

| Figure 5.1  | Pseudo-differential gain stage with cross-coupled inverters                       | 56 |

| Figure 5.2  | Proposed differential linear optical receiver                                     | 57 |

| Figure 5.3  | Architecture of the proposed differential optical receiver in [36]                | 58 |

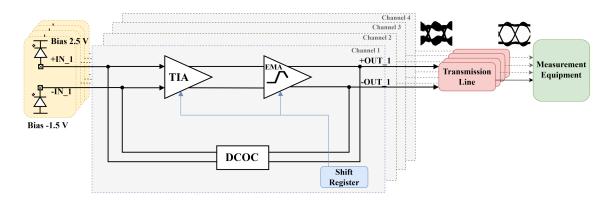

| Figure 5.4  | Block diagram of the 4-channel differential optical receiver                      | 59 |

| Figure 5.5  | Layout of the main circuitry of a single channel of the proposed differential     |    |

| optica      | al receiver                                                                       | 60 |

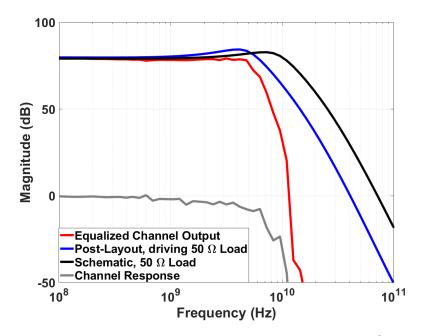

| Figure 5.6  | Frequency response of the proposed optical receiver driving a 50 $\Omega$ load,   |    |

| showi       | n for both schematic-level and post-layout simulations (black and blue), the      |    |

| measi       | ured high-speed PCB trace channel model (grey), and the cascaded response         |    |

| of the      | optical receiver and the channel (red)                                            | 61 |

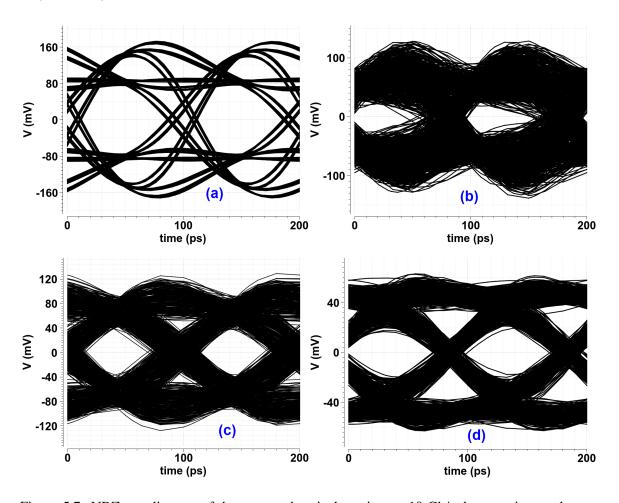

| Figure 5.7  | NRZ eye diagram of the proposed optical receiver at 10 Gb/s data rate in          |    |

| post-l      | ayout simulation a) when driving a 50 $\Omega$ load, b) at channel's input, c) at |    |

| chann       | nel's output, and d) at channel's output when the IAFB is enabled                 | 62 |

| Figure 5.8  | PAM-4 eye diagram of the proposed linear optical receiver in post-layout                  |    |

|-------------|-------------------------------------------------------------------------------------------|----|

| simula      | ation at 10 Gb/s at the output of the measured high-speed PCB trace channel               |    |

| model       | L                                                                                         | 63 |

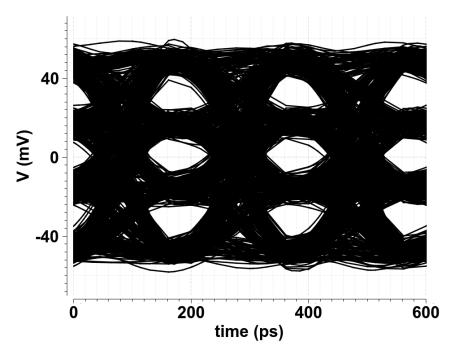

| Figure 5.9  | NRZ eye diagram of the proposed optical receiver at 5 Gb/s in post-layout                 |    |

| simul       | ation a) when driving a 50 $\Omega$ load, b) at the output of the very high-loss channel. | 64 |

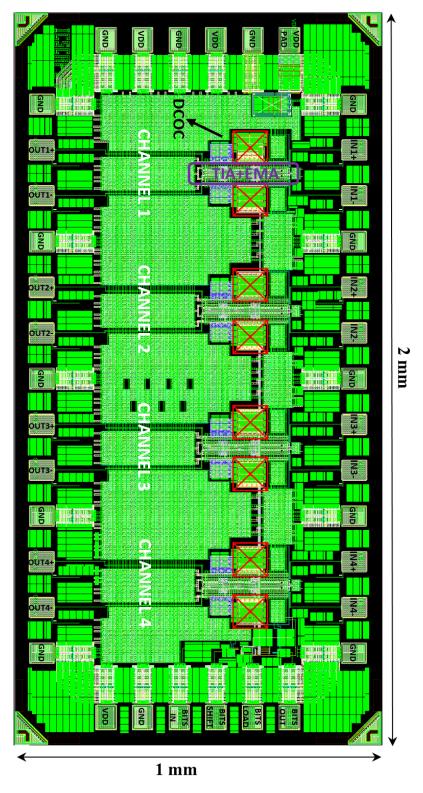

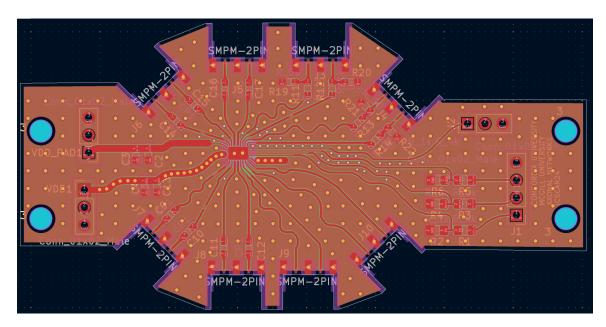

| Figure 5.10 | Complete layout of the proposed 4-channel optical receiver with I/O pads                  |    |

| and a       | seal ring.                                                                                | 65 |

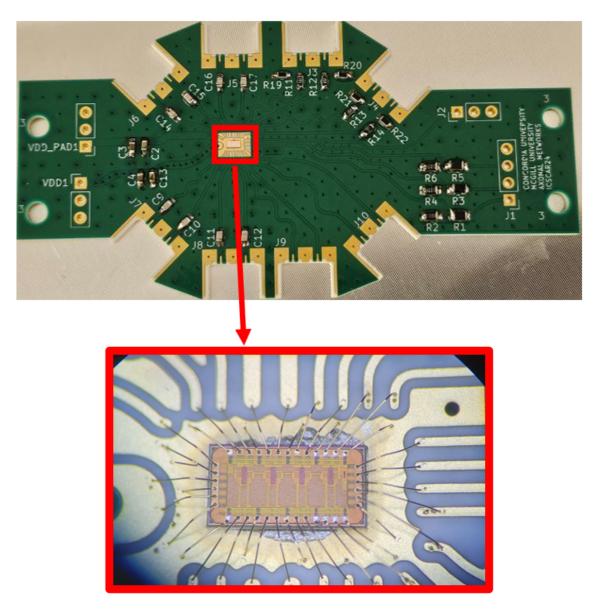

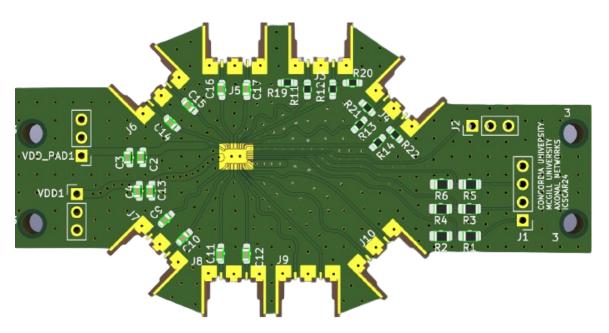

| Figure 5.11 | Fabricated chip of the proposed 4-channel linear optical receiver wire-bonded             |    |

| onto t      | he designed high-speed PCB for electrical measurements                                    | 66 |

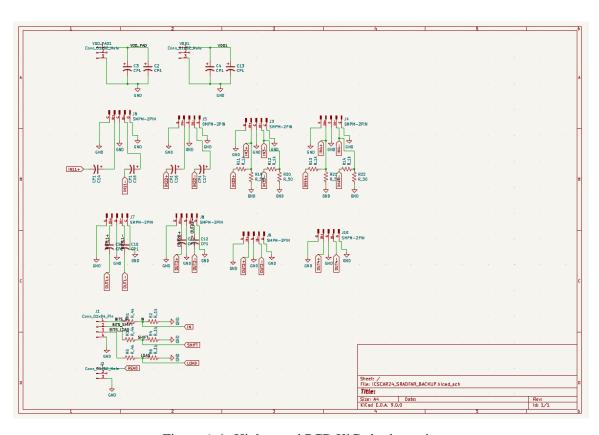

| Figure A.1  | High-speed PCB KiCad schematic                                                            | 73 |

| Figure A.2  | High-speed PCB KiCad design                                                               | 74 |

| Figure A.3  | High-speed PCB KiCad 3D design                                                            | 74 |

# **List of Tables**

| Table 3.1 | Simulation Results Comparison Summary                                    | 43 |

|-----------|--------------------------------------------------------------------------|----|

| Table 5.1 | Device Dimensions and Component Values in the 4-Channel Optical Receiver |    |

| Desi      | gn                                                                       | 64 |

| Table 6.1 | The Performance Comparison and Summary                                   | 69 |

# **Chapter 1**

# Introduction

The exponential growth of internet traffic, driven by bandwidth-intensive services and AI applications, has necessitated a rapid expansion of data centers, which rely heavily on high-speed interconnects. AI workloads require massive data movement between GPUs, TPUs, and storage systems, demanding ultra-fast, high-bandwidth communication. However, electrical interconnects often become bottlenecks due to their high-frequency losses and limited capacity. As a result, optical interconnects have become essential, offering superior speed, reliability, and power efficiency compared to their electrical counterparts [1]. Optical transceivers enable high-bandwidth, low-latency connections in data centers, allowing efficient model training and inference, which is critical for modern AI applications.

To increase data transmission rates in optical links, intensity modulation and direct detection (IMDD) transceivers are widely used. While 2-level pulse amplitude modulation (PAM-2), often referred to non-return-to-zero (NRZ) signaling, requires a very large circuit bandwidth at high speeds, multi-level modulation formats such as PAM-4 reduce this bandwidth requirement. PAM-4, which encodes two bits per symbol using four discrete amplitude levels, has become widely adopted due to its improved spectral efficiency over PAM-2 (NRZ). This allows for a higher data rate while maintaining reduced bandwidth requirements. However, PAM-4 introduces new design challenges, including reduced signal level separation, increased susceptibility to noise and distortion, and stringent linearity requirements for the analog front-end [2].

Optical receiver design is critical in PAM-4 systems, as the eye diagram becomes both vertically

and horizontally compressed. To ensure proper detection, an analog front-end must exhibit high linearity, wide bandwidth, and low noise. Due to the possibility of insufficient Transimpedance Amplifier (TIA) gain to achieve logical levels, a high-gain amplifier, known as the main amplifier (MA), is required after the TIA. The nonlinearity of the optical receiver is primarily dictated by the final stages of the MA. Among various topologies, the Cherry-Hooper (CH) amplifier is a common choice due to its wide bandwidth [3,4]. However, studies have shown that its linearity is insufficient for PAM-4 optical links [5]. To address this, the  $g_m/g_m$  amplifier topology, which consists of a transconductor followed by a diode-connected inverter load to cancel transconductor nonlinearities, has been explored [5–7]. While  $g_m/g_m$  amplifiers offer superior linearity, their bandwidth is lower than that of CH amplifiers, necessitating the use of bandwidth extension techniques, especially in less advanced technologies.

### 1.1 Motivation

High-speed optical communication systems require efficient receiver designs to handle increasing data rates and bandwidth demands. Designing optical receivers for high-speed NRZ signaling demands an extremely wide bandwidth, which presents significant design challenges. To overcome this limitation, multi-level signaling schemes such as PAM-4 have been introduced.

In PAM-4 systems, receiver design is particularly challenging due to the reduced vertical and horizontal eye openings, which degrade signal integrity. The analog front-end must exhibit high linearity, wide bandwidth, and low noise to accurately recover the transmitted signal. Furthermore, to be competitive with NRZ receivers, PAM-4 receivers must operate at low voltages, demonstrate robustness against process and temperature variations, and minimize chip area [5].

A key limitation in the design of PAM-4 optical receivers is the nonlinear behavior of conventional main amplifiers, which can distort the signal levels and degrade system performance. The Cherry-Hooper amplifier, a common choice for broadband design, offers a wide bandwidth but lacks sufficient linearity for PAM-4. In contrast, the  $g_m/g_m$ -based topology demonstrates enhanced linearity, making it a promising candidate for linear optical receivers. However, its limited bandwidth necessitates additional extension techniques to meet high-speed performance requirements.

To enhance bandwidth without relying on passive inductors, the interleaving active feedback (IAFB) technique [8] has been developed. In this work, the combination of a  $g_m/g_m$ -based main amplifier with IAFB results in a highly linear PAM-4 main amplifier, making it a strong candidate for high-speed optical receiver designs.

As data rates continue to rise, signal degradation due to channel impairments, such as attenuation, inter-symbol interference (ISI), and impedance mismatches, becomes increasingly significant, leading to elevated bit error rates and degraded system performance. In linear-drive optical receiver architectures, the front-end amplifier drives a lossy channel before the signal reaches the clock and data recovery (CDR) unit. This intermediate channel introduces frequency-dependent loss and ISI, especially for multilevel signaling schemes like PAM-4. To mitigate these effects, receiver-side equalization becomes essential. This work focuses on the design of an equalizing main amplifier that incorporates high-frequency peaking (HFP) within the front-end itself [9]. By embedding equalization directly into the main amplifier, this approach reduces the need for a separate continuous-time linear equalizer (CTLE) stage, enabling a more compact and energy-efficient receiver solution.

#### 1.2 Publications and Contributions of the Author

- S. Radfar and G. Cowan, "Linearity Enhancement for Inverter-Based Optical Receivers Employing Active Feedback," IEEE Midwest Symp. on Circuits and Systems (MWSCAS), Springfield, MA, USA, 2024.

- 2) S. Radfar and G. Cowan, "Interleaving Active Feedback in Inverter-Based Optical Receivers for Bandwidth Extension and Linearity Improvement," IEEE Int. Symp. on Circuits and Systems (ISCAS), Singapore, 2024.

# 1.3 Thesis Organization

Chapter 2 begins by introducing modulation formats, eye diagrams, and key linearity metrics used in optical transceivers, such as Total Harmonic Distortion (THD) and Ratio Level Mismatch (RLM), to evaluate performance in PAM-4 systems. Then it reviews inverter-based optical receiver designs and examines a bandwidth extension technique that avoids the use of inductors. Finally,

the chapter discusses methods for embedding equalization capability into the receiver front-end to compensate for losses introduced by the downstream electrical channel, with a particular emphasis on HFP.

In **Chapter 3**, a methodology for designing and further enhancing a highly linear main amplifier is proposed, with simulation results presented and compared to the commonly used Cherry-Hooper amplifier topology and the  $g_m/g_m$ -based topology.

Chapter 4 explores an approach to equalizing the main amplifier without using a separate CTLE stage. The technique is implemented on the proposed highly linear main amplifier, enhancing the signal integrity of the structure when used with a lossy transmission line. This results in a power-and area-efficient linear main amplifier.

**Chapter 5** discusses the implementation of the proposed linear optical receiver with the equalizing main amplifier, designed for fabrication in 65 nm CMOS technology. The method for making the structure fully differential is detailed, and post-layout simulation results are presented.

Finally, **Chapter 6** compares the proposed linear optical receiver to existing ones, summarizes the thesis, and presents future objectives.

# **Chapter 2**

# **Background and Literature Review**

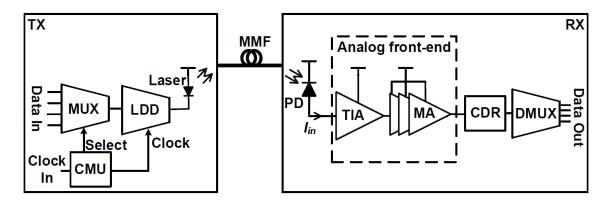

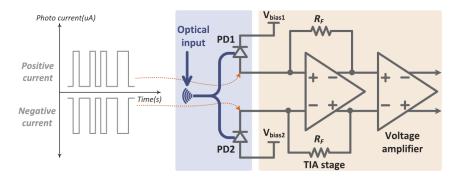

Illustrated in Fig. 2.1, the initial stage of a standard CMOS optical receiver (RX) consists of a photodiode (PD) followed by a transimpedance amplifier (TIA). Since the PD generates a small current and most subsequent processing is voltage-based, the TIA is employed to convert the input current into a voltage signal. However, the TIA output may not provide sufficient voltage swing to reach logical levels, necessitating the use of a high-gain stage, known as the main amplifier (MA). The MA significantly influences the overall linearity of the receiver and plays a critical role in its performance. In this chapter, after introducing two main concepts and linearity metrics in optical transceivers, we explore inverter-based MA designs and review existing methods from the literature aimed at improving linearity, bandwidth, and reducing inter-symbol interference (ISI).

Figure 2.1: Block diagram of a typical short-reach optical link [9].

### 2.1 Modulation Formats

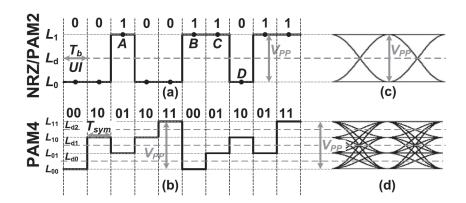

In high-speed communication systems, digital data is commonly transmitted using pulse amplitude modulation (PAM), as described in Fig. 2.2 [10]. The simplest form is PAM-2, also known as non-return-to-zero (NRZ) (Fig. 2.2 (a)), where each symbol represents a single bit using two distinct signal levels, typically a high level for logic 1 ( $L_1$ ) and a low level for logic 0 ( $L_0$ ). The signal maintains its level throughout the bit period ( $T_b$ ), which is why it is referred to as "non-return-to-zero". NRZ is decoded at the receiver by comparing the signal against a single threshold level ( $L_d$ ) once per unit interval (UI). To achieve higher data rates without reducing the UI, a more advanced modulation scheme like PAM-4 can be used, which is shown in Fig. 2.2 (b). PAM-4 transmits two bits per symbol ( $T_{sym}$ ) by dividing the full voltage or optical power range into four distinct levels, thus requiring three decision thresholds for decoding denoted as  $L_{d0}$ ,  $L_{d1}$ , and  $L_{d2}$  in Fig. 2.2 (b). While PAM-4 doubles the data rate for a given symbol rate, it also reduces the spacing between signal levels, demanding better noise performance and linearity. Consequently, PAM-4 offers bandwidth efficiency at the cost of increased design complexity and signal integrity challenges.

Figure 2.2: Time-domain representations of signals used to encode binary data include: (a) an example of an NRZ (PAM-2), (b) an example of a PAM-4 signal, (c) the eye diagram corresponding to PAM-2, and (d) the eye diagram for PAM-4 [10].

# 2.2 Eye Diagram

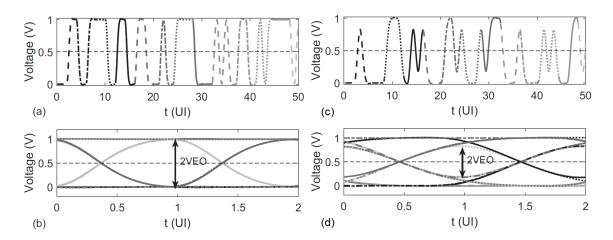

The eye diagram is a widely used technique for evaluating signal quality in wired communication systems. As shown in Fig. 2.3 (a) and (c), segments of the signal shown with different line

styles (typically two UIs long) are extracted and superimposed to create a composite view, resulting in the eye diagram illustrated in Fig. 2.3 (b) and (d) [10]. This visualization provides insight into signal integrity and timing behavior. In the absence of inter-symbol interference (ISI), as in Fig. 2.3 (a) and (b), the sampled values corresponding to logic 1 at the decision point (usually at 1 UI) are tightly clustered around a consistent voltage level, independent of the surrounding bit pattern. In contrast, when ISI is present, as demonstrated in Fig. 2.3 (c) and (d), the amplitude of a logic 1 may vary depending on the previous bits. For instance, a 1 following a sequence of 0s may appear with reduced amplitude compared to a 1 following another 1, indicating distortion and degradation in signal quality.

In Fig. 2.3 (b) and (d), the vertical eye opening (VEO) is defined as the distance between the minimum '1' level (or maximum '0' level) and the decision threshold  $L_d$ . This implies that the total distance between the maximum '0' and minimum '1' levels is technically twice the VEO. Although the decision threshold is assumed to lie at the midpoint of the eye in this context, throughout this thesis, we refer to the full distance from the maximum '0' to the minimum '1' level simply as the VEO. As illustrated in Fig. 2.3 (d), significant ISI introduced by the channel or circuit reduces the eye opening.

Figure 2.3: Formation of an eye diagram by dividing the signal into segments of two unit intervals long: (a) NRZ signal; (b) resulting eye diagram, indicating minimal inter-symbol interference (ISI); (c) NRZ signal; (d) corresponding eye diagram, showing noticeable ISI effects [10].

### 2.3 Linearity Metrics in Optical Transceivers

#### **2.3.1** Total Harmonic Distortion (THD)

Nonlinearities in the optical receiver introduce residual ISI that cannot be fully corrected, even with optimized equalization parameters. Linearity is typically characterized by metrics such as total harmonic distortion at specific input amplitudes and frequencies.

If we approximate the input/output characteristic of a memoryless analog circuit by the following polynomial

$$y(t) = \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t) + \dots, \tag{2.1}$$

when the value of x is small, the output y(t) can be approximated as

$$y(t) = \alpha_1 x$$

.

This approximation suggests that  $\alpha_1$  represents the small-signal gain near x=0. We can assess the nonlinearity of a circuit by introducing a sinusoidal input and analyzing the harmonic components present in the output signal [11]. Substituting  $x(t) = A\cos(\omega t)$  in (2.1) yields

$$y(t) = \alpha_1 A \cos(\omega t) + \alpha_2 A^2 \cos^2(\omega t) + \alpha_3 A^3 \cos^3(\omega t) + \dots$$

=  $\alpha_1 A \cos(\omega t) + \frac{\alpha_2 A^2}{2} [1 + \cos(2\omega t)] + \frac{\alpha_3 A^3}{4} [3\cos(\omega t) + \cos(3\omega t)] + \dots$  (2.2)

In (2.2), we observe that higher-order terms generate higher harmonics. Specifically, evenorder terms produce even harmonics, while odd-order terms generate odd harmonics. The  $n^{th}$ -order harmonic distortion ( $HD_n$ ) is defined as the ratio of the amplitude of the  $n^{th}$  component to that of the fundamental.

The linearity of an analog circuit is typically quantified by the square root of the sum of squares for all orders of harmonic distortion [11]. This metric is commonly referred to as "total harmonic

distortion" (THD) and can be defined as

$$THD = \sqrt{HD_2^2 + HD_3^2 + \dots}$$

(2.3)

Reported linear optical receiver designs typically maintain THD below 2.5% for output swings ranging from  $400 \, mV_{pp}$  to  $600 \, mV_{pp}$  [5,12]. Some works demonstrate enhanced linearity, achieving THD as low as 1.77% at  $500 \, mV_{pp}$  [13], while others report up to 5% THD at higher swings [14]. These results suggest a practical target of <2.5% THD for high-speed linear receivers operating in this swing range.

#### 2.3.2 Ratio Level Mismatch (RLM)

The bit error rate (BER), defined as the ratio of incorrectly received bits to the total number of transmitted bits, is a critical metric for evaluating the reliability of a communication link. A BER of  $10^{-12}$  is commonly targeted in high-speed systems. However, PAM-4 signaling inherently exhibits a smaller vertical eye opening compared to NRZ, making it more difficult to achieve such low BER values, especially in high-loss channels. Transitioning from a two-level signal (NRZ) to a four-level signal (PAM-4) requires adjustments to both the transmitter and receiver to accommodate the increased signal complexity [10].

In a PAM-4 system, the transmitter must generate four distinct signal levels instead of the two used in NRZ. At the receiver end, the signal must be processed using three decision thresholds to distinguish between these levels, unlike NRZ, which only requires one. Furthermore, the transceiver must maintain a high degree of linearity to accurately interpret the multi-level signal.

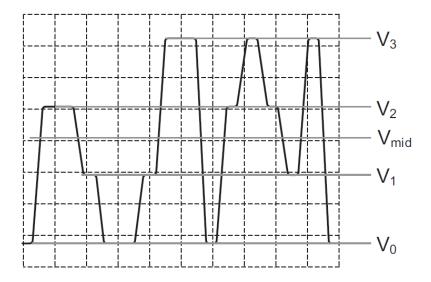

A common metric used to evaluate PAM-4 transceiver performance is ratio level mismatch (RLM), which measures how evenly spaced the four signal levels are. In a steady-state condition, where ISI is minimal due to the transmission of enough consecutive identical digits, the signal levels are denoted as  $V_0$  through  $V_3$  (Fig. 2.4) [10]. The midpoint of the signal,  $V_{\rm mid}$ , represents the average of the highest and lowest levels

$$V_{\text{mid}} = \frac{V_3 + V_0}{2} \tag{2.4}$$

Based on this midpoint, the relative signal levels for the "01" and "10" symbols, denoted as  $ES_1$  and  $ES_2$ , are calculated using the following expressions

$$ES_1 = \frac{V_1 - V_{\text{mid}}}{V_0 - V_{\text{mid}}}, \quad ES_2 = \frac{V_2 - V_{\text{mid}}}{V_3 - V_{\text{mid}}}$$

(2.5)

Figure 2.4: Signal level definitions for ratio level mismatch [10].

Ideally, these values should both equal 1/3 to ensure symmetrical spacing. The RLM value is defined as the minimum of four terms

$$RLM = \min(3ES_1, 3ES_2, (2 - 3ES_1), (2 - 3ES_2))$$

(2.6)

When the signal levels are perfectly balanced, RLM reaches its ideal value of 1. In practical systems, RLM values above 0.95 are generally considered acceptable. However, while useful, RLM does not account for other critical aspects of signal integrity, such as ISI or timing misalignment between the sub-eyes [10].

## 2.4 Inverter-based Main Amplifiers

Although inverters are commonly linked to digital circuits, the inverter has proven to be a highly adaptable analog building block for a wide range of applications, as extensively explored in [15,16]. Its class AB operation enables it to achieve an effective compromise between low noise, low power consumption, and broad bandwidth, while still maintaining a satisfactory level of linearity. In the following sections, we will examine one of the most commonly used inverter-based main amplifiers in optical receivers and then explore a suitable alternative for PAM-4 optical receivers.

### 2.4.1 Cherry-Hooper (CH) Amplifier

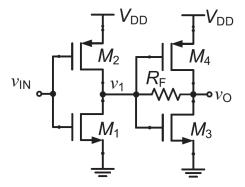

The Cherry-Hooper (CH) amplifier based on CMOS inverters consists of two cascaded inverters, shown in Fig. 2.5. A resistive feedback,  $R_F$ , is applied around the second stage to enhance the amplifier's bandwidth. In this configuration, the first stage operates as a transconductance stage, converting input voltage to current, while the second inverter together with the feedback resistor realizes a transresistance amplifier. This inverter-based CH topology is extensively utilized across multiple data rates and CMOS process nodes, making it a versatile solution in high-speed analog circuit design [3, 17, 18].

Figure 2.5: Inverter-based Cherry-Hooper amplifier.

The CH amplifier is widely favored in high-speed analog design for its superior bandwidth performance compared to simpler topologies, such as cascaded first-order gain stages. While two cascaded stages typically produce real poles, the CH configuration introduces complex conjugate poles, resulting in a peaked frequency response that effectively extends the bandwidth. Designers can also adjust the damping factor by tuning circuit parameters such as the transconductance,  $g_m$ , feedback resistance,  $R_F$ , and parasitic capacitances, offering valuable flexibility in optimizing amplifier performance [10].

Another key advantage of the CH topology is its efficient handling of capacitive loading. The second stage operates as a transresistance amplifier, performing current-to-voltage conversion while presenting a lower equivalent output resistance than a simple resistive load. This reduced output resistance minimizes the RC time constant, contributing to further bandwidth enhancement [10]. However, the CH amplifier lacks the high linearity required for PAM-4 optical receivers, necessitating the use of a more linear gain stage that also maintains high bandwidth.

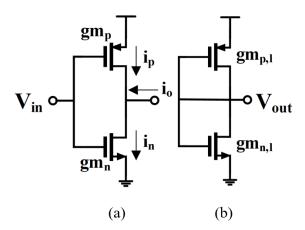

## **2.4.2** $g_m/g_m$ Amplifier

When an analog inverter (Fig. 2.6 (a)) is biased at the midpoint between the maximum and minimum power supply voltages, both the n-channel and p-channel transistors operate in the saturation region. In this condition, the inverter has the maximum possible gain and serves as a linear transconductor [16]. The overall transconductance of the block is the result of adding the small-signal transconductance of both NMOS and PMOS transistors. This simple two-transistor circuit has only two nodes, i.e., input and output nodes. Therefore, it removes the concern of additional parasitic poles that might degrade the bandwidth [5]. The efficiency of the analog inverter transconductor in terms of noise, power consumption, and bandwidth, all while maintaining a satisfactory level of linearity performance, has made it a foundational cell that can be applied to accomplish various functions [7, 19, 20]. The output current of the transconductor of Fig. 2.6 (a) can be written as

Figure 2.6: Schematic diagram of (a) a transconductor, and (b) diode-connected inverter.

$$i_o = i_n - i_p \approx (k_n V_{\text{ov,n}} + k_p V_{\text{ov,p}}) v_i + \left(\frac{k_n}{2} - \frac{k_p}{2}\right) v_i^2$$

(2.7)

where  $k=\mu C_{\rm ox}\left(\frac{W}{L}\right)$  and  $V_{\rm ov}=V_{\rm GS}-V_t$ . This expression is derived under the square-law assumption of MOSFETs operating in saturation. The current-voltage equation shows that if  $k_n=k_p$ , the second-order nonlinearity cancels out. In the event of a mismatch, the second-order nonlinearity is only proportionate to  $k_n=k_p$ . Mobility degradation caused by the transverse electric field and channel length modulation results in the creation of odd-order nonlinearities. These nonlinearities can pose challenges, especially when operating in low-supply voltages [5]. Fig. 2.6 (b) represents a shorted (diode-connected) inverter. [5] demonstrates that an inverter-based transconductor loaded with a diode-connected inverter called a  $g_m/g_m$  amplifier (Fig. 2.7), offers much better linearity compared to the CH amplifiers. The reason for calling it a  $g_m/g_m$  amplifier is that the total gain of the block in Fig. 2.7 is equal to  $G_m/G_{m,L}$  where  $G_m$  and  $G_{m,L}$  denote the total transconductances of the transconductor and load stages, respectively. A detailed discussion of the higher linearity of the  $g_m/g_m$  amplifier can be found in [16]. When NMOS and PMOS transistors have nearly equal threshold voltages, negligible channel length modulation, and operate in saturation, the output voltage of the unity gain  $g_m/g_m$  amplifier in Fig. 2.7 can be expressed as [21]

$$V_{\text{out}} = V_{\text{DD}} - V_{\text{in}} \tag{2.8}$$

Figure 2.7: Block diagram of the  $g_m/g_m$  amplifier.

demonstrating a linear voltage transfer characteristic. Importantly, this linearity holds as long as the nonlinearity of the transistors is predominantly odd-order.

Fig. 2.8 illustrates three different inverter-based pseudo-differential amplifier designs to investigate their linearity according to their loads. The sizes of the inverters are chosen to have a DC gain of 2 in all structures and equal power consumption. Moreover, these amplifiers operate with a 1 V power supply and have the same differential peak-to-peak swing of 600 mV.

Figure 2.8: Comparison of different amplifier topologies. (a) Resistive load amplifier. (b)  $g_m/g_m$  amplifier. (c) TAS-TIS (Cherry-Hooper) amplifier [5].

The load of the transconductor of Fig. 2.8 (a) is an ideal resistor. The second transconductor is loaded with diode-connected inverters, and the third one is the well-known CH amplifier, which is widely used in optical receivers. The linearity of these structures is shown in Fig. 2.9 in terms of harmonic levels and THD. As can be seen, the transconductor with diode-connected inverter loads  $(g_m/g_m)$  topology) has the best linearity, i.e., the lowest 3rd-order harmonic level and THD. On the other hand, the Cherry-Hooper amplifier represents the worst linearity. Other than high linearity, the superiority of using the diode-connected inverter loads instead of an actual resistor in Fig. 2.8 (a) and (b) is occupying a much smaller area and also eliminating one design parameter, i.e.,

resistance, to have the desired gain, bandwidth, and output impedance [5]. Moreover, the  $g_m/g_m$  architecture exhibits better PVT insensitivity, as both transconductances, i.e.,  $G_m$  and  $G_{m,L}$ , are typically affected similarly.

Figure 2.9: Linearity comparison of different amplifier topologies: (a) Harmonic levels, (b) THD [5].

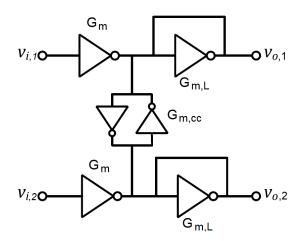

In a pseudo-differential structure (Fig. 2.10), the  $g_m/g_m$  amplifiers exhibit common-mode gain, which can degrade performance. To address this issue, cross-coupled inverters are introduced. The use of diode-connected and cross-coupled inverters was first introduced by [6], but was later analyzed in greater depth by [15], particularly in the context of transconductors. Fig. 2.11 illustrates the linear transconductance structure proposed by [15], designed for use in linear, tunable integrators in very high-frequency continuous-time integrated filters. In this configuration, Inv4,5 serve as diode-connected load inverters, while Inv3,6 function as the cross-coupled inverters.

Figure 2.10:  $g_m/g_m$  amplifiers in a pseudo-differential structure.

Figure 2.11: Linear transconductance structure proposed in [15].

As shown in Fig. 2.12, [5] proposed a linear optical receiver for  $100 \text{ Gb/s/}\lambda \text{ PAM-4}$  optical links based on the  $g_m/g_m$  amplifier. Similar to Nauta's design, cross-coupled inverters were employed to achieve common-mode rejection and minimize mismatch. Additionally, an inverter-based single-to-differential converter with a diode-connected inverter load was used, offering lower phase offset and group delay compared to configurations with an open inverter load [5].

Figure 2.12: Schematic of the proposed linear optical receiver in [5].

The discussed literature demonstrates that the  $g_m/g_m$  amplifier can be an excellent candidate for use as a linear main amplifier. However, compared to the CH amplifier, it suffers from limited bandwidth due to the repeated real poles in the cascaded  $g_m/g_m$  structure, which compresses the bandwidth more than the complex-conjugate poles of a second-order CH amplifier. Therefore, bandwidth extension techniques must be employed to compensate for this limitation. [5] addressed this by placing an inductor within the feedback loop of the TIA, effectively shielding the input capacitance of the inverter and thereby achieving high bandwidth with minimal in-band peaking. While this method is effective, the use of inductors results in significant chip area consumption, motivating the exploration of inductor-less alternatives.

# 2.5 Inductorless Bandwidth Extension Techniques

### 2.5.1 Interleaving Active Feedback (IAFB)

Incorporating negative feedback into the MA circuitry enhances both linearity and bandwidth. This section examines how active negative feedback can be leveraged for bandwidth extension. By applying this technique, it is possible to achieve high bandwidth without the use of inductors.

In a cascade of amplifiers used in the MA circuit, the total bandwidth can be written as [22]

$$BW_{\text{tot}} = BW_{\text{cell}} \cdot \sqrt[2m]{\sqrt[n]{2} - 1}$$

(2.9)

where n is the number of cascaded stages with  $m^{th}$ -order Butterworth frequency response, and  $BW_{cell}$  is the bandwidth of a unit amplifier cell. Moreover, if  $A_{tot}$  is defined as the total gain of the MA circuit, the gain-bandwidth product of the unit gain cell will be equal to [23]

$$GBW_{\text{cell}} = \frac{BW_{\text{tot}}}{\sqrt[2m]{\sqrt[n]{2} - 1}} \cdot \sqrt[n]{A_{\text{tot}}}$$

(2.10)

Fig. 2.13 shows the required gain-bandwidth product of a unit amplifier cell within the MA circuit for m=1,2, and 3 when  $A_{\rm tot}=40\,{\rm dB}$  and  $BW_{\rm tot}=10\,{\rm GHz}$ . Given this plot, the larger n, the less the required gain-bandwidth product of a unit cell. However, by increasing the number of identical cascaded stages, the descending trend of the required GBW<sub>cell</sub> does not continue and starts to saturate. It should be noted that by having a large n, the MA's power consumption increases, and the MA's input-referred noise degrades due to the reduced gain per unit gain cell [8]. Therefore, it is important to choose an optimal value for n, typically 4 or 5.

Figure 2.13: The relationship between the GBW product and the number of stages for  $A_{\text{tot}} = 40 \text{ dB}$  and  $BW_{\text{tot}} = 10 \text{ GHz}$  [8].

Another conclusion that can be extracted from Fig. 2.13 is that reaching the required gain-bandwidth product using first-order amplifier cells within the MA circuit is not practical in a standard 180 nm CMOS technology, which has an  $f_T$  of 50 GHz [8]. However, in the cascading of four second- and third-order 10 dB gain stages, the required GBW<sub>cell</sub> is 49 and 41 GHz, respectively. Based on the transition frequency of the technology, without using the inductive peaking technique, the required specifications cannot be met even by employing second-order gain stages [22]. The IAFB bandwidth extension technique is investigated for the cascade of third-order amplifier cells.

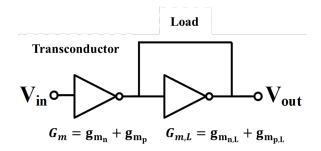

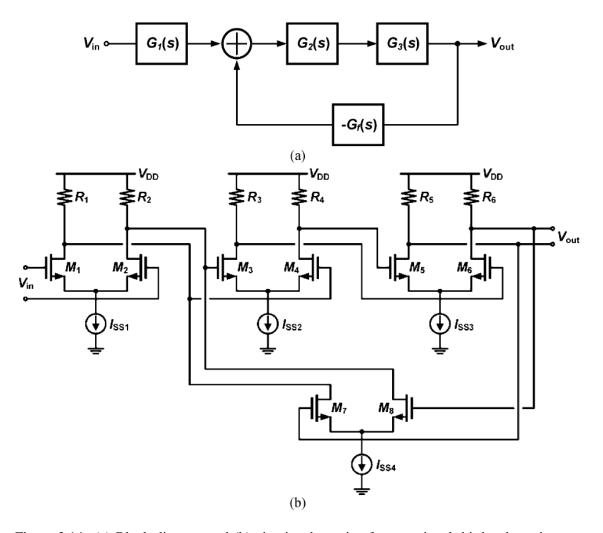

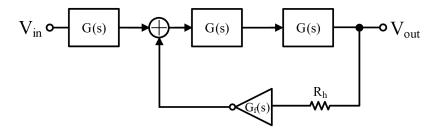

Fig. 2.14 shows the block diagram and circuit schematic of a conventional third-order amplifier, which includes active feedback. If each first-order gain cell and active feedback cell is characterized by the transfer functions of

$$G_{1-3}(s) = \frac{G_m R}{1 + sRC}, \quad G_f(s) = \frac{G_{mf} R}{1 + sRC}$$

(2.11)

respectively, then the overall transfer function of the third-order system can be written as [8]

$$H_{3rd}(s) = \frac{G_1(s) \cdot G_2(s) \cdot G_3(s)}{1 + G_1(s) \cdot G_2(s) \cdot G_f(s)} = \frac{G_m^3 R^3}{(1 + sRC)^3 + G_m^2 G_{mf} R^3}$$

(2.12)

where  $G_m$  and  $G_{mf}$  denote the transconductance of each differential pair, and R and C are the resistive and capacitive loads per stage.

If  $\omega_0=\frac{1}{RC}$ ,  $A_0=G_mR$ , and  $\beta=G_{mf}R$ , equation 2.12 can be simplified to [8]

$$H_{3\text{rd}}(s) = \frac{A_0^3}{\left(1 + \frac{s}{\omega_0}\right)^3 + A_0^2 \beta}$$

(2.13)

which has one non-dominant real pole and two dominant conjugate poles.

Fig. 2.15 (a) shows the trend of gain-bandwidth characteristics as a function of the feedback gain  $\beta$  with  $A_0 = 2.5$ . Obviously, by increasing  $\beta$ , the normalized -3 dB bandwidth increases, but it leads to reduced gain. Fig. 2.15 (b) is illustrated to investigate the gain flatness of this third-order system. According to this plot, as  $\beta$  increases, gain peaking increases as well. Hence, while applying active feedback to third-order gain stages can improve the bandwidth, it cannot be considered a useful technique for extending bandwidth because it causes a noticeable increase in

Figure 2.14: (a) Block diagram and (b) circuit schematic of conventional third-order gain stages with active feedback [8].

the associated gain peaking [8].

Figure 2.15: Variations of (a) gain and normalized bandwidth, and (b) gain peaking of the conventional third-order amplifier by increasing the feedback gain  $\beta$  [8].

A practical technique to enhance the bandwidth while maintaining gain flatness is to apply IAFB to the system. Fig. 2.16 illustrates the cascaded third-order stages with interleaving active feedback.

Figure 2.16: Block diagram of the cascaded third-order stages with the proposed interleaving feedback in [8].

The transfer function of the system is given by [8]

$$H(s) = \frac{G^6(s)}{1 + 3G^2(s)G_f(s) + G^4(s)G_f^2(s)}$$

(2.14)

which can be written as two third-order transfer functions with different feedback gains as follows

$$H(s) = H_A(s) \cdot H_B(s) = \frac{G_3(s)}{1 + 2.62 G_2(s) G_f(s)} \cdot \frac{G_3(s)}{1 + 0.38 G_2(s) G_f(s)}$$

(2.15)

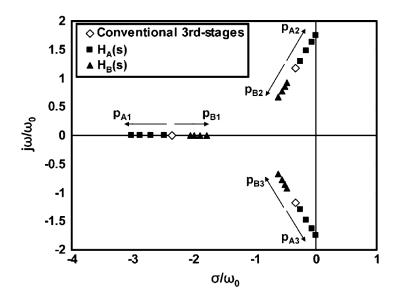

In 2.15,  $H_A(s)$  and  $H_B(s)$  represent two conventional third-order systems similar to Fig. 2.14 (a), but with dissimilar feedback gains of -2.62 and -0.38, respectively. With different feedback gains, now each  $H_A(s)$  and  $H_B(s)$  has three poles with different locations than 2.12. In other words, pole splitting occurs, as shown in Fig. 2.17.

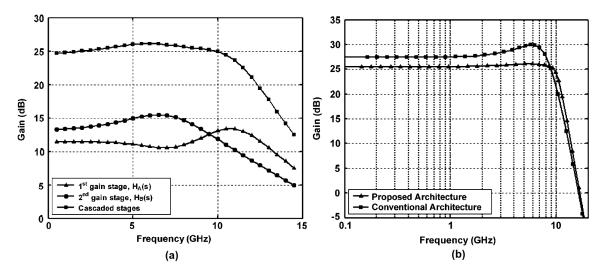

Fig. 2.18 (a) shows that with  $\beta=0.3$ ,  $H_A(s)$  and  $H_B(s)$  represent a relatively large gain peaking. However, cascading these two third-order stages leads to a considerable improvement in gain flatness. Moreover, the frequency response of the cascaded third-order gain stages with and without IAFB is illustrated in Fig. 2.18 (b). Given this plot, both bandwidth and gain flatness are noticeably improved.

Figure 2.17: Pole splitting behavior of the proposed feedback technique in [8].

Figure 2.18: (a) Simulated frequency response of the cascaded architecture with nonuniform third-order gain stages; (b) Simulated frequency response of the cascaded third-order gain stages [8].

# 2.6 Equalizing the Electrical Channel in Optical Receivers

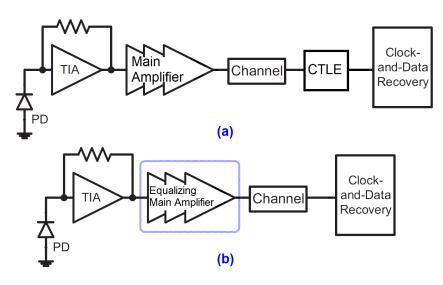

Fig. 2.19 (a) illustrates the block diagram of an optical receiver system. Following the main amplifier stage, the signal passes through an electrical channel, which may represent a PCB trace or a coaxial cable in an electrical link. As the data rate increases, the pulse response of the channel begins to exhibit significant ISI, a common issue in high-speed electrical link standards [10].

Receiver-side equalization is essential in modern high-speed data transmission systems to compensate for signal degradations caused by the transmission channel, particularly in systems using copper interconnects [24]. Without equalization, these impairments can lead to significant signal distortion, resulting in eye closure and increased BER, thereby degrading overall system performance and reliability. To address this, a continuous-time linear equalizer (CTLE) is typically employed after the channel.

Figure 2.19: Block diagram of an optical receiver link: (a) employing a CTLE stage for equalization, and (b) utilizing an equalizing main amplifier to compensate for channel losses.

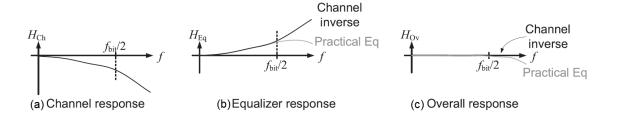

As illustrated in Fig. 2.20, the CTLE compensates for the channel's frequency-dependent losses by approximating the inverse of the channel's frequency response, thereby flattening the overall response up to the Nyquist frequency (i.e.,  $f_{bit/2}$ ). This frequency shaping enhances the high-frequency components of the received signal, which are increasingly attenuated as data rates rise, leading to ISI and degraded signal integrity. Due to practical design tradeoffs, the CTLE provides only partial equalization, with the remaining compensation typically handled by a decision feedback equalizer (DFE) [24].

Figure 2.20: Equalization as channel inversion: (a) frequency response of the channel; (b) frequency response of an equalizer; (c) overall frequency response [10].

The CTLE achieves its frequency-shaping characteristics by introducing a zero and a pole in its transfer function, typically implemented through resistive and capacitive degeneration in a differential amplifier [24]. The placement of these frequencies governs the equalizer's ability to provide gain at higher frequencies while preserving unity gain at low frequencies. The eye diagram at the CTLE output is then analyzed to ensure signal clarity, and a programmable boost factor is introduced to fine-tune the high-frequency gain [24]. Since a single stage offers limited boosting, multiple CTLE stages may be cascaded, but at the cost of increased power consumption and potential bandwidth reduction. To address these limitations, inductive peaking is often employed to extend bandwidth without significantly increasing power usage [25]. This technique enhances high-frequency performance by mitigating the effects of parasitic capacitances, albeit at the expense of a larger chip area due to the use of passive inductors.

In the following, we explore an approach that integrates equalization directly into the main amplifier without introducing additional circuitry or passive elements in the optical receiver, thereby reducing power consumption and chip area.

#### 2.6.1 Equalizing Main Amplifier (EMA)

A beneficial approach in high-speed optical receivers is to incorporate high-frequency peaking (HFP) in the MA to extend bandwidth. Properly tuned HFP, particularly near the Nyquist frequency, helps compensate for bandwidth limitations caused by other components in the optical link, thereby improving signal integrity. These bandwidth constraints often arise due to parasitic capacitances, packaging effects, and the limited gain-bandwidth product of active devices. By boosting the high-frequency components of the signal, HFP ensures signal integrity and maintains the overall link

performance.

A traditional method for achieving HFP, as described in [26], involves using passive inductors in both shunt and series configurations between stages of a programmable gain amplifier. This technique compensates for performance variations in multi-mode fibers and extends bandwidth. However, passive inductors occupy large silicon areas, complicate integration, and may introduce substrate coupling issues, making them less desirable for compact and power-efficient designs.

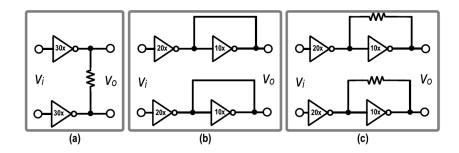

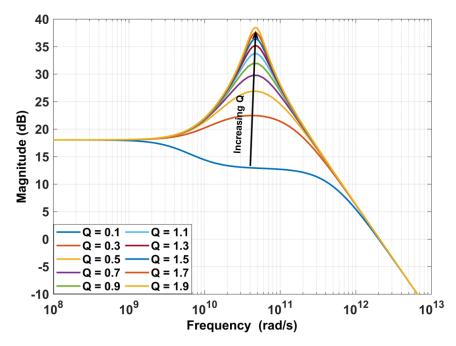

To overcome these challenges, [27] proposes an active feedback-based MA design that introduces a carefully placed pole in the feedback loop. Rather than extending the MA's intrinsic bandwidth, this approach compensates for the limited bandwidth of the preceding TIA, thereby enhancing the overall frequency response of the receiver front-end. By eliminating the need for passive inductors, it reduces chip area and avoids substrate coupling issues. The feedback pole is strategically placed to provide gain peaking in the desired frequency range, ensuring sufficient signal amplification at high frequencies.

Integrating HFP within the main amplifier stage itself allows the MA to perform the role of a CTLE. As illustrated in Fig. 2.19 (b), this integration simplifies the receiver front-end architecture by removing the need for a separate CTLE block. The result is a more compact design with lower power consumption, which is critical for high-speed optical communication systems where energy efficiency is a primary concern. Additionally, the equalizing main amplifier (EMA) contributes to improved signal-to-noise ratio (SNR) and jitter tolerance. Compensating for high-frequency losses ensures cleaner eye diagrams and more reliable data recovery at the clock and data recovery (CDR) unit.

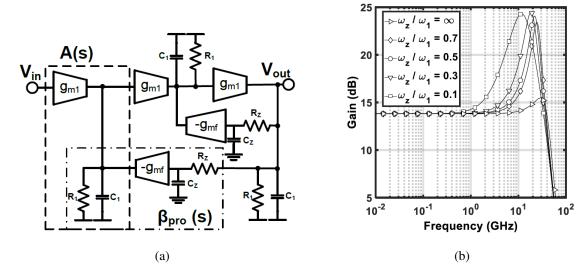

Figure 2.21 (a) presents the block diagram of the third-order nested feedback gain stage using the HFP technique proposed in [27]. The first-order gain cell, A(s), is represented by the transconductance of the input device  $g_{m1}$ , load resistance  $R_1$ , and load capacitance  $C_1$ . The adjustable active feedback cell,  $\beta_{\text{pro}}(s)$ , is modeled by the transconductance  $-g_{mf}$ .

Figure 2.21: Block diagram of (a) the third-order EMA in [27] with a LPF inserted in each feedback path (b) amplitude response of the EMA for various ratios of  $\omega_Z/\omega_1$ .

In this design, two poles are introduced in the feedback loops using  $R_Z$  resistors to create an adjustable HFP while maintaining the low-frequency gain. The transfer function of the third-order nested feedback block is described in 2.16, where  $A_1=g_{m1}R_1$  and  $\omega_1=(R_1C_1)^{-1}$  represent the DC gain and cutoff frequency of the first-order gain cell, respectively. The DC feedback gain is given by  $\beta_1=g_mfR_1$ , and  $\omega_Z=(R_ZC_Z)^{-1}$  is the cutoff frequency of the low-pass filter introduced, which is assumed to have minimal loading on the output node.

$$H_{EMA}(s) = \frac{A_1^3 \left(\frac{s}{\omega_Z} + 1\right)}{\left(\frac{s}{\omega_1} + 1\right)^3 \left(\frac{s}{\omega_Z} + 1\right) + A_1 \beta_1 \left(\frac{s}{\omega_1} + 1\right) + A_1^2 \beta_1}$$

(2.16)

The effect of varying  $\omega_Z$  on the amplitude response of the proposed EMA is shown in Fig. 2.21 (b). For a fixed  $\beta_1$ , HFP can be introduced independently of the low-frequency gain. As  $\omega_Z$  decreases, the peak of the amplitude response shifts to a lower frequency.

This approach integrates the equalization functionality into the gain stage, enabling the circuit to maintain the performance advantages of conventional equalizer-based designs while enhancing energy efficiency by eliminating the need for a separate equalizer stage.

## 2.7 Conclusion

In this chapter, we focused on inverter-based main amplifiers for optical receivers. According to linearity metrics such as THD, the  $g_m/g_m$  structure exhibits superior linearity compared to the widely used CH amplifier. However, the CH topology provides a wider bandwidth. To overcome this limitation, we investigated an inductorless bandwidth extension technique for the  $g_m/g_m$  amplifier, aiming to avoid the additional chip area associated with inductors. Lastly, to enhance the eye diagram and mitigate ISI, two receiver-side equalization strategies were explored: incorporating CTLE stages and implementing HFP within the analog front end. Among these, equalizing the main amplifier through HFP proved to be a promising solution for linear-drive systems, as it effectively compensates for channel losses without adding additional CTLE stages or increasing power consumption in the receiver front end.

# Chapter 3

# **Linear Main Amplifier**

The preceding sections have reviewed the fundamental concepts of high-speed, linear optical receiver design, covering existing linearization techniques, bandwidth enhancement methods, and equalization approaches reported in the literature. From this chapter onward, we present the proposed receiver architecture and the associated design techniques, which form the original contributions of this thesis.

In this chapter, we propose a highly linear PAM-4 optical receiver based on the  $g_m/g_m$  topology, implemented in 65 nm CMOS technology. The interleaving active feedback (IAFB) technique [8] enhances bandwidth without relying on passive inductors. By combining  $g_m/g_m$  main amplifiers with the IAFB technique, the proposed receiver achieves a data rate of 50 Gb/s (25 GBaud/s) while maintaining a total harmonic distortion (THD) of less than 2% at a 500  $mV_{pp}$  output swing. To further improve linearity, resistive voltage dividers are incorporated into the feedback loops, reducing THD to below 0.6% at the same output swing.

# 3.1 $g_m/g_m$ -based Main Amplifier Design

## 3.1.1 Bandwidth Extension Technique

Implementing negative feedback can improve both the bandwidth and linearity of a circuit. The poles can be shifted to higher values, and the pole quality factor (Q) can be improved by introducing negative feedback, thus extending the bandwidth [8]. As nonlinearity can be perceived

Figure 3.1: Block diagram of the proposed PAM-4 linear main amplifier using  $g_m/g_m$ -based amplifiers and IAFB technique.

as fluctuations in the small-signal gain with the input level, negative feedback is also anticipated to suppress such variations, resulting in improved linearity for the closed-loop system [11]. [8] introduces the IAFB technique to enhance the bandwidth of the cascaded third-order amplifier cells through the pole-splitting phenomenon. While negative active feedback can improve bandwidth, it can increase gain peaking [8]. Nevertheless, the IAFB technique can increase bandwidth with reasonable gain flatness through a combination of low and high Q pole pairs.

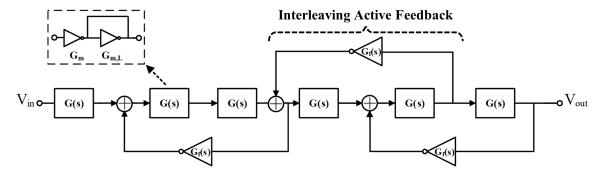

Fig. 3.1 shows the proposed linear main amplifier based on the  $g_m/g_m$  topology and the IAFB technique. This configuration comprises six stages of inverter-based transconductors, known for their high linearity, loaded by diode-connected inverters, and employs IAFB to boost bandwidth. Notably, this design exhibits considerably superior linearity compared to a six-stage cascade of Cherry-Hooper (CH) amplifiers with equivalent input voltage and gain. Furthermore, the IAFB approach has led to a broader bandwidth when compared to its CH amplifier-based counterpart. The subsequent section delves into the design methodology and simulation results of the proposed linear main amplifier and offers a comparison with the widely employed CH amplifier.

## 3.2 Design Methodology and Simulation Results

#### 3.2.1 PMOS to NMOS Ratio

The proposed linear main amplifier is designed in 65 nm CMOS technology. It operates with a 1 V supply voltage. Let us first consider Fig. 3.1 without any feedback. In the open-loop design,

each  $g_m/g_m$  cell is designed to have a gain of 2. In advanced technology like 16 nm FinFet, the n-channel and p-channel transistors have identical mobility and threshold voltage. Moreover, the  $g_m$  of the transistors is about 10 times larger than  $g_{ds}$ , which makes it possible to ignore channel length modulation [21]. Hence, if the size of the load inverter in Fig. 2.7 is reduced to half that of the transconductor, achieving a gain of 2 is straightforward. However, in 65 nm CMOS technology, the mobility of the NMOS and PMOS transistors is not the same, and  $g_{ds}$  must be considered in the calculations.

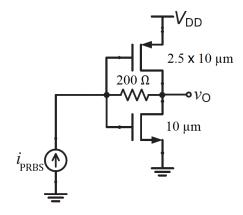

Based on our simulations, the  $g_m/g_m$  amplifier has the highest linearity when the PMOS transistor's width is 2.5 times larger than NMOS's. Therefore, considering this ratio and channel length modulation, in the open-loop design, the width of NMOS in the transconductor and load inverters is  $10~\mu m$  and  $2.7~\mu m$ , respectively. The PMOS transistors are 2.5 times larger than their corresponding NMOS transistors. Using these dimensions, each  $g_m/g_m$  amplifier in Fig. 3.1 has a gain of 2, giving a total gain of 64 for the six cascaded  $g_m/g_m$  amplifiers.

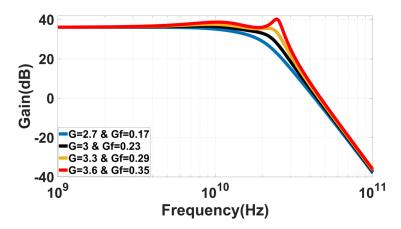

#### 3.2.2 Gain Selection

The next step is to add the negative active feedback loops and the IAFB to the circuit, which all consist of single inverters. To have a reasonable comparison, using the transfer function of (2.14), the total gain of the proposed circuit is kept at 64 by increasing the gain of each  $g_m/g_m$  cell.

As previously mentioned, negative active feedback causes gain peaking, and IAFB reduces it. Fig. 3.2 shows the frequency response of the proposed design with different combinations of gains for the forward blocks (G(s)) and feedback inverters  $(G_f(s))$  to have a total gain of 64. It can be seen that increasing the gain of the feedback inverters increases both bandwidth and gain peaking. The amount of gain peaking for the different combinations of G(0) and  $G_f(0)$  is demonstrated in Fig. 3.2.

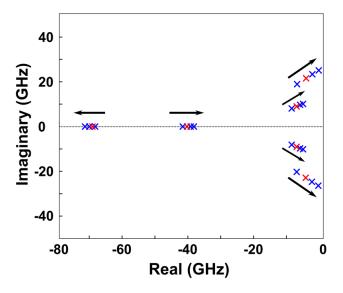

IAFB can result in significant pole-splitting if the loop gain becomes excessively large. This pole-splitting can lead to a situation where a pair of conjugate poles shifts into the right half-plane, making the system unstable. Fig. 3.3 illustrates the pole locations of the proposed main amplifier for different combinations of G(s) and  $G_f(s)$  DC gains to have a total gain of 64. This plot shows that the far-right pair of conjugate poles moves toward the right half-plane by increasing the feedback

gain and the forward gain. To ensure a stable system, the poles of the transfer function of (2.14) must have negative real parts. Therefore, we must be careful in choosing the design point to avoid instability and unbounded dynamic response.

Figure 3.2: Gain peaking for different combinations of G(0) and  $G_f(0)$  to have a total gain of 64.

Figure 3.3: Pole location variations of the proposed design for different combinations of G(s) and  $G_f(s)$  to have a total gain of 64. The red markers represent the pole locations of the design with G(0)=3 and  $G_f(0)=0.23$ .

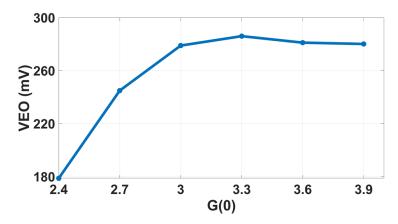

Fig. 3.4 shows how vertical eye-opening (VEO) changes in different combinations of G(0) and  $G_f(0)$ . The largest VEO happens at G(0)=3.3 and  $G_f(0)$ =0.29, but as G(0) and  $G_f(0)$  increase, the jitter of the eye diagram gets larger. Based on these trade-offs, the forward and feedback gains are set to G(0) = 3 and  $G_f(0)$  = 0.23, resulting in NMOS transistor widths of 1.28  $\mu$ m and 723 nm for

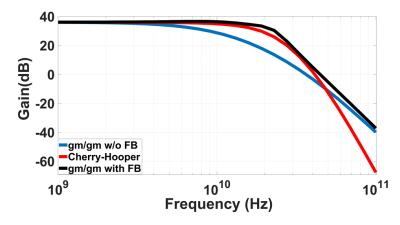

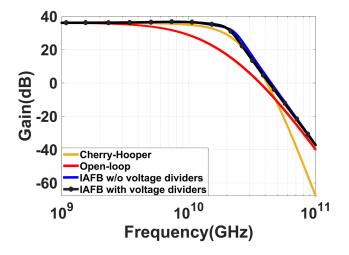

the transconductor and diode-connected inverters, respectively. To compare the frequency response of the  $g_m/g_m$ -based design with and without feedback and the CH-based design, Fig. 3.5 is plotted. It is evident that the feedback has significantly improved the bandwidth of the  $g_m/g_m$  circuit. The ratio of 2.5 between PMOS and NMOS transistor widths is kept in all three configurations, and each CH stage is designed to have a gain of 2. At the same total gain of 64 (36 dB), the  $g_m/g_m$ -based circuit with three negative active feedback has the widest bandwidth.

Figure 3.4: VEO variations of the six-stage  $g_m/g_m$  design with IAFB in different combinations of G(0) and  $G_f(0)$ .

Figure 3.5: Frequency response of the six-stage  $g_m/g_m$ -based design with and without IAFB at G(0)=3 and  $G_f(0)$ =0.23, and six-stage CH-based amplifier.

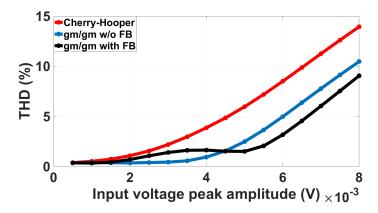

To investigate the linearity of the  $g_m/g_m$ -based design with and without feedback and the CH amplifier, the THD of these topologies is plotted in Fig. 3.6 for a range of input voltage. The CH amplifier has the worst linearity (highest THD) in the entire range of the input voltage. The linearity

of the open-loop  $g_m/g_m$  amplifier is the best in small input voltage amplitudes while adding feed-back improves linearity at higher voltages. Linear feedback usually improves linearity. However, when applied to inverter-based designs, the feedback network, built from the same circuit elements as the forward gain path, introduces nonlinearity. Specifically, the feedback inverter whose input is connected to the overall output sees a very large input signal, exceeding its linear range. Its distortion cannot be easily eliminated, explaining why the IAFB design does not exhibit better linearity across all input voltages compared to the open-loop design. We also designed and simulated the fully differential configuration of the proposed design and expected to see a noticeable decrease in the THD due to the elimination of the even-order harmonics. However, the amount of the THD reduction was insignificant.

Figure 3.6: THD of the six-stage  $g_m/g_m$ -based design with and without IAFB at G(0)=3 and  $G_f(0)$ =0.23, and six-stage CH-based main amplifier.

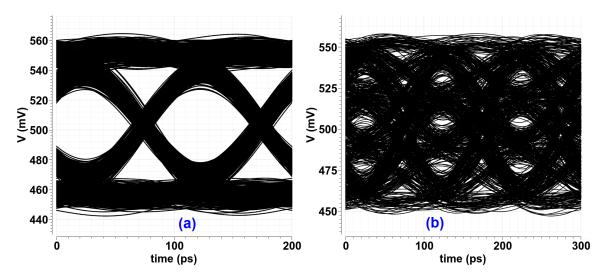

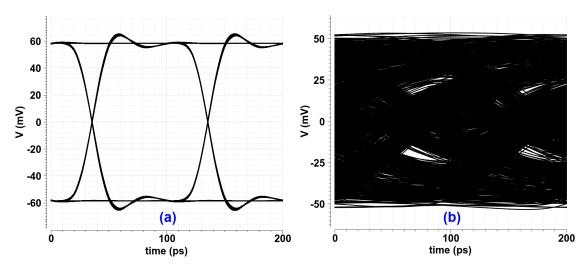

A pseudo-random bit source (PRBS) is given to a conventional shunt-feedback TIA input (shown in Fig. 3.7), and the output of the TIA is connected to the proposed main amplifier. Among various TIA circuit topologies, the shunt-feedback TIA is the most widely used due to its superior gain and noise performance [28]. Fig. 3.8 (a) displays the eye diagram of the circuit in the NRZ signaling scheme at G(0)=3 and  $G_f(0)=0.23$ , and Fig. 3.8 (b) represents it in PAM-4 format with a unit interval (UI) of 40 ps. The circuit configuration remains unchanged between the two signaling formats. Fig. 3.9 (a) and (b) demonstrates the NRZ and PAM-4 eye diagrams for CH-based topology, respectively. Apart from the higher bandwidth and better linearity than the CH-based design, the proposed design also represents a larger VEO.

Figure 3.7: Schematic of the shunt-feedback TIA used in the optical receiver.

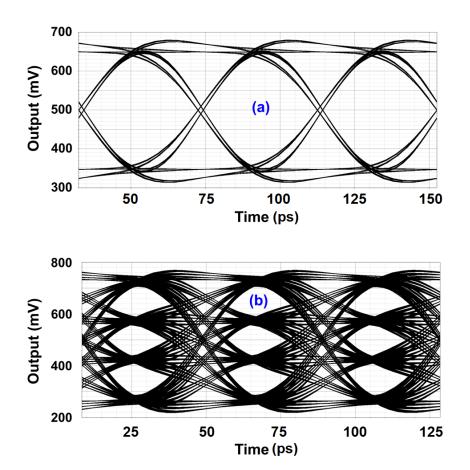

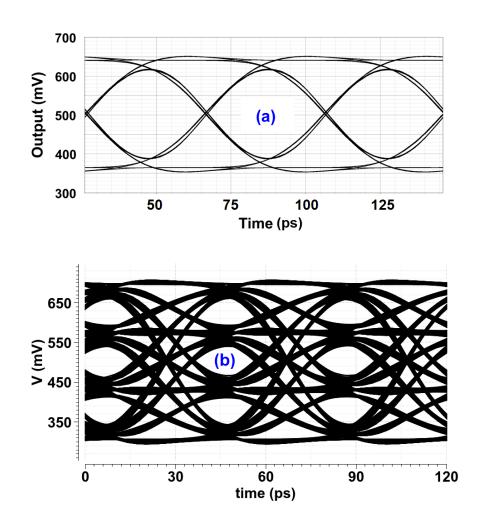

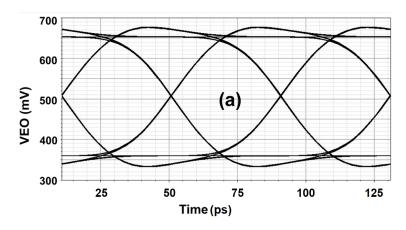

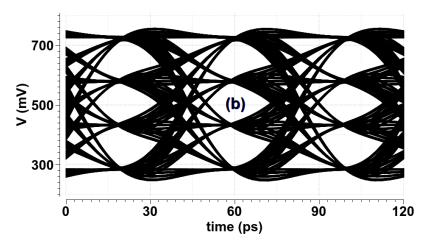

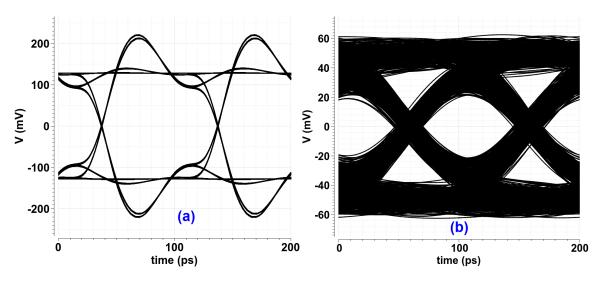

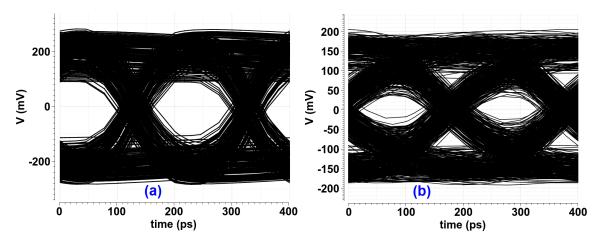

Figure 3.8: The eye diagrams of the proposed design in a) NRZ, b) PAM-4 at G(0)=3 and  $G_f(0)$ =0.23 with 40 ps of UI.

Figure 3.9: The eye diagrams of the CH-based design in a) NRZ, b) PAM-4 with 40 ps of UI.

## 3.3 Linearity Improvement

In Fig. 3.6, it was noted that the linearity of the open-loop six-stage  $g_m/g_m$  amplifier performed best at lower input voltage amplitudes, while the addition of feedback improved linearity at higher voltages. The degraded linearity of the proposed design at smaller input voltages is mainly due to the feedback inverter receiving a large signal from the overall output, causing it to operate outside its linear range and introduce distortion that the feedback loop cannot suppress. The following section introduces a method to enhance the linearity of the proposed design at lower input voltage amplitudes.

## 3.3.1 Effect of Third Nonlinear Coefficients on THD

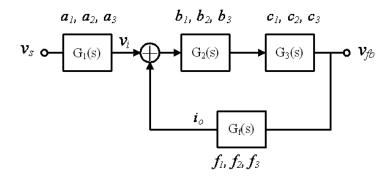

Fig. 3.10 shows the block diagram of a third-order amplifier with three identical gain cells. In the absence of feedback, the transfer characteristic of a basic amplifier (e.g.  $G_1$  in Fig. 3.10) using power series can be expressed as the following polynomial [29]

$$v_i = a_1 v_s + a_2 v_s^2 + a_3 v_s^3 + \dots (3.1)$$