# Machine Learning based Memory Load Approximation

Alain Aoun

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy (Electrical and Computer Engineering) at

Concordia University

Montréal, Québec, Canada

July 2025

© Alain Aoun, 2025

### CONCORDIA UNIVERSITY

### School of Graduate Studies

This is to certify that the thesis prepared

| By:            | Mr. Alain Aoun                                                     |                                |

|----------------|--------------------------------------------------------------------|--------------------------------|

| Entitled:      | Machine Learning based Memo                                        | ory Load Approximation         |

| and submitted  | d in partial fulfillment of the requirement                        | nts for the degree of          |

| Docto          | or of Philosophy (Electrical and Co                                | omputer Engineering)           |

| complies with  | n the regulations of this University and                           | l meets the accepted standards |

| with respect t | to originality and quality.                                        |                                |

| Signed by the  | Final Examining Committee:                                         |                                |

|                | Dr. Name of the Chair                                              | Chair                          |

|                | Dr. Jean Pierre David                                              | External Examiner              |

|                | Dr. Otmane Ait Mohamed                                             | Examiner                       |

|                | Dr. Sebastien Lebeux                                               | Examiner                       |

|                | Dr. Joey Paquet                                                    | Examiner                       |

|                | Dr. Sofiène Tahar                                                  | Supervisor                     |

| Approved by    | Abdelwahab Hamou-Lhadj, Chair<br>Department of Electrical and Comp | outer Engineering              |

| July 2025      |                                                                    |                                |

Mourad Debbabi, Dean

Faculty of Engineering and Computer Science

### Abstract

#### Machine Learning based Memory Load Approximation

Alain Aoun, Ph.D.

Concordia University, 2025

Modern computing applications demand ever-increasing performance and energy efficiency. However, conventional processor architectures frequently stall while waiting for data retrieval from memory, creating a bottleneck known as the *memory wall*. Over the past decades, various approaches such as speculative prefetching, load value prediction, and hardware caching have been proposed to mitigate this limitation. While these techniques yield moderate gains, they often rely on rigid hardware logic or simple pattern matching, which struggle with the irregular, data-driven workloads typical of contemporary multimedia and machine learning applications.

This thesis propose to use Machine Learning (ML) to speculate load values and reduce memory accesses. The proposed method is grounded in the principles of Approximate Computing (AC), where minor inaccuracies are accepted in exchange for improvements in performance or efficiency. To this end, we introduce an ML-based Load Value Approximation (ML-LVA) approach, which predicts the values of memory loads to reduce access latency. The ML-LVA is trained offline to generate a compact predictor that captures patterns in image and audio data, enabling accurate value prediction during runtime without the need for continual retraining. By learning

spatial correlations among adjacent data values, the proposed ML-LVA effectively anticipates memory contents, thereby reducing stalls and improving overall system performance in online deployment.

We have implemented the proposed ML-LVA framework both in software and hardware. The software variant targets existing processors lacking reconfigurability, as well as systems with tight area or power constraints that prohibit adding custom hardware. It operates as a callable subroutine designed for seamless integration without modifying the processor architecture. The software implementation was tested on an x86 processor in the GEM5 simulator. On the other hand, the hardware-based implementation integrates the proposed ML-LVA as a dedicated accelerator accessed via a custom instruction, offering tighter pipeline integration, lower latency, and enhanced efficiency for newly designed systems. The hardware-based ML-LVA was implemented in CVA6, which is an open source RISC-V processor. The synthesis results conducted in Cadence Innovus showed that the overhead of the added accelerator is marginal.

Experimental results conducted on audio and image processing workloads demonstrate that the proposed ML-LVA accelerates memory access by over  $6\times$ , resulting in application speedups up to  $2.45\times$ . Additionally, even when predicting up to 95% of loads, the output fidelity remains within perceptual thresholds. Subsequently, the proposed ML-LVA outperforms state-of-the-art LVAs in terms of performance and quality. The ML-LVA achieves these results with only a 5% area overhead and less than 1% power increase in silicon.

In loving memory of my grandmother, who passed away during my PhD, and my Godfather, my guardian angels,

To my father, my mother, my sister and brothers.

## Acknowledgments

First, I would like to thank my supervisor, Prof. Sofiène Tahar, for his valuable feedback, support, and encouragement throughout my PhD thesis. He was always available to share his experience and knowledge. His continuous belief and push through the proposed PhD project was a great essence in delivering the final output we present in this thesis. Moreover, during my study under his supervision, I learned a lot about research which helped me improving my abilities in this field. Also, I am grateful for the valuable feedback that I received from a colleague who became a dear friend, Dr. Mahmoud Masadeh. The priceless brainstorming sessions, the long meetings and sharing of his experience throughout my research were corner stones of my work. I am extremely grateful and forever beholden for his continuous availability and encouragement throughout my PhD journey.

I am also deeply grateful for Prof. Abdallah Kassem who was my supervisor at Notre Dame University for my undergraduate studies. Through his endless support and feedback, I acquired a lot of knowledge that was the essence for my graduate studies.

I would also like to express my gratitude for Dr. Jean Pierre David, Dr. Joey Paquet, Dr. Otmane Ait Mohamed, and Dr Sebastian Lebeux for serving on my advisory thesis committee and taking the time from their busy schedules to read and evaluate my thesis.

I am deeply thankful to my friends and colleagues at HVG, Elif, Kübra, and Oumaima, whose support made the PhD journey significantly more manageable. Thank you for listening patiently, thinking out loud with me, offering valuable advice, and always making the lab feel like home with a warm cup of tea and cookies at just the right time.

Finally, with all my love and gratitude, I want to thank my dearest family, Farid, Mona, Georges, Youssef and Lamia. Your unconditional love, endless patience, and unwavering support have been my anchor throughout this journey and every stage of my life. There were moments of doubt, exhaustion, and frustration, but your constant presence reminded me of my strength and my purpose. You believed in me when I struggled to believe in myself, and that made all the difference. Your sacrifices, encouragement, and quiet resilience have shaped who I am today. This PhD is not just my achievement—it is ours. I am forever grateful to you, and I carry your love with me always.

Last but by no mean the least, I would like to thank Michêle for the endless love, support and patient throughout my PhD study. Her constant encouragement made even the hardest days feel lighter, and I am truly grateful to have had her by my side.

# Table of Contents

| Li       | st of                | Figure | es                       | xii |

|----------|----------------------|--------|--------------------------|-----|

| Li       | st of                | Tables | s                        | xv  |

| Li       | ${f st}$ of          | Abbre  | eviations                | xvi |

| 1        | Intr                 | oducti | ion                      | 1   |

|          | 1.1                  | Motiva | ation                    | 1   |

|          | 1.2                  | State- | of-the-Art               | 6   |

|          |                      | 1.2.1  | Approximate Memory       | 7   |

|          |                      | 1.2.2  | ML-based Prefetching     | 8   |

|          |                      | 1.2.3  | Load Value Speculation   | 9   |

|          |                      | 1.2.4  | Load Value Approximation | 10  |

|          | 1.3                  | Proble | em Statement             | 12  |

|          | 1.4                  | Propo  | sed Methodology          | 13  |

|          | 1.5                  | Thesis | Contributions            | 19  |

|          | 1.6                  | Thesis | organization             | 21  |

| <b>2</b> | $\operatorname{Pre}$ | limina | ry                       | 23  |

|          | 2.1                  | Introd | uction                   | 23  |

|   | 2.2  | Evalua | ating Approximate Computing  | 24 |

|---|------|--------|------------------------------|----|

|   | 2.3  | Multin | media Applications           | 28 |

| 3 | ML   | -based | Load Value Predictor         | 34 |

|   | 3.1  | Introd | luction                      | 34 |

|   | 3.2  | Traini | ng Method                    | 36 |

|   | 3.3  | Datas  | et Selection and ML Training | 39 |

|   |      | 3.3.1  | Dataset Selection            | 39 |

|   |      | 3.3.2  | ML Training                  | 42 |

|   | 3.4  | Qualit | by Assessment                | 46 |

|   |      | 3.4.1  | Image Processing             | 46 |

|   |      |        | 3.4.1.1 Image Blending       | 46 |

|   |      |        | 3.4.1.2 Image Inversion      | 51 |

|   |      |        | 3.4.1.3 Image Binarization   | 53 |

|   |      | 3.4.2  | Audio Processing             | 55 |

|   |      |        | 3.4.2.1 Audio Blending       | 56 |

|   |      |        | 3.4.2.2 Audio Inversion      | 58 |

|   |      |        | 3.4.2.3 Audio Binarization   | 60 |

|   |      | 3.4.3  | Comparison with Related Work | 61 |

|   | 3.5  | Summ   | nary                         | 64 |

| 4 | Soft | wara l | Implementation of the ML-LVA | 66 |

| 1 | 4.1  |        | luction                      | 66 |

|   | 4.1  |        |                              | 68 |

|   | 4.2  | -      | sed Methodology              | 70 |

|   |      |        | mentation of the Predictor   |    |

|   | 4.4  | restin | g Environment                | 72 |

|    | 4.5                                           | Perfor                                                                | mance Analysis               | 76                                                        |

|----|-----------------------------------------------|-----------------------------------------------------------------------|------------------------------|-----------------------------------------------------------|

|    | 4.6                                           | Exper                                                                 | imental Results              | 78                                                        |

|    |                                               | 4.6.1                                                                 | Image Processing             | 79                                                        |

|    |                                               |                                                                       | 4.6.1.1 Image Blending       | 79                                                        |

|    |                                               |                                                                       | 4.6.1.2 Image Inversion      | 82                                                        |

|    |                                               |                                                                       | 4.6.1.3 Image Binarization   | 83                                                        |

|    |                                               | 4.6.2                                                                 | Audio Processing             | 86                                                        |

|    |                                               |                                                                       | 4.6.2.1 Audio Blending       | 87                                                        |

|    |                                               |                                                                       | 4.6.2.2 Audio Inversion      | 89                                                        |

|    |                                               |                                                                       | 4.6.2.3 Audio Binarization   | 91                                                        |

|    |                                               | 4.6.3                                                                 | Comparison with Related Work | 93                                                        |

|    | 4.7                                           | Summ                                                                  | ary                          | 94                                                        |

|    |                                               |                                                                       |                              |                                                           |

| 5  | Har                                           | dware                                                                 | Implementation of the ML-LVA | 97                                                        |

| 5  |                                               |                                                                       | Implementation of the ML-LVA | 9 <b>7</b>                                                |

| 5  | 5.1                                           | Introd                                                                | uction                       | 97                                                        |

| 5  | 5.1<br>5.2                                    | Introd<br>Propo                                                       | uction                       | 97<br>99                                                  |

| 5  | 5.1                                           | Introd<br>Propo<br>Hardw                                              | sed Methodology              | 97<br>99<br>103                                           |

| 5  | 5.1<br>5.2                                    | Introd<br>Propo<br>Hardw<br>5.3.1                                     | uction                       | 97<br>99<br>103<br>104                                    |

| 5  | 5.1<br>5.2                                    | Introd<br>Propo<br>Hardw                                              | uction                       | 97<br>99<br>103<br>104<br>107                             |

| 5  | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>Propo<br>Hardw<br>5.3.1<br>5.3.2<br>5.3.3                   | uction                       | 97<br>99<br>103<br>104<br>107<br>110                      |

| 5  | 5.1<br>5.2                                    | Introd<br>Propo<br>Hardw<br>5.3.1<br>5.3.2<br>5.3.3<br>Exper          | uction                       | 97<br>99<br>103<br>104<br>107<br>110<br>112               |

| 5  | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>Propo<br>Hardw<br>5.3.1<br>5.3.2<br>5.3.3                   | nuction                      | 97<br>99<br>103<br>104<br>107<br>110<br>112<br>113        |

| วั | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>Propo<br>Hardw<br>5.3.1<br>5.3.2<br>5.3.3<br>Exper          | uction                       | 97<br>99<br>103<br>104<br>107<br>110<br>112<br>113<br>113 |

| 5  | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>Propo<br>Hardw<br>5.3.1<br>5.3.2<br>5.3.3<br>Exper<br>5.4.1 | uction                       | 97<br>99<br>103<br>104<br>107<br>110<br>112<br>113<br>113 |

| 5  | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>Propo<br>Hardw<br>5.3.1<br>5.3.2<br>5.3.3<br>Exper          | uction                       | 97<br>99<br>103<br>104<br>107<br>110<br>112<br>113<br>113 |

|    |       |          | 5.4.2.2 Audio Inversion      |   | 119 |

|----|-------|----------|------------------------------|---|-----|

|    |       | 5.4.3    | Comparison with Related Work |   | 121 |

|    |       | 5.4.4    | Overhead Measures            | • | 122 |

|    | 5.5   | Summ     | nary                         |   | 122 |

| 6  | Cor   | nclusio  | on and Future Work           |   | 125 |

|    | 001   | iciasio. | and radia Work               |   |     |

|    | 6.1   | Conclu   | lusion                       |   | 125 |

|    | 6.2   | Future   | re Work                      |   | 128 |

|    |       |          |                              |   |     |

| Re | efere | nces     |                              |   | 133 |

| Bi | ogra  | nhv      |                              |   | 143 |

# List of Figures

| 1.1  | Normalized Performance over the Years [3]                               | 2  |

|------|-------------------------------------------------------------------------|----|

| 1.2  | Memory Bandwidth when Increasing the Number of Thread versus the        |    |

|      | Ideal Scalability [13]                                                  | 4  |

| 1.3  | Methodology of the Proposed ML-LVA                                      | 15 |

| 1.4  | Deployment Framework for the Proposed Methodology                       | 17 |

| 3.1  | Training Method of the Proposed ML-LVA                                  | 38 |

| 3.2  | Prediction Sequence                                                     | 39 |

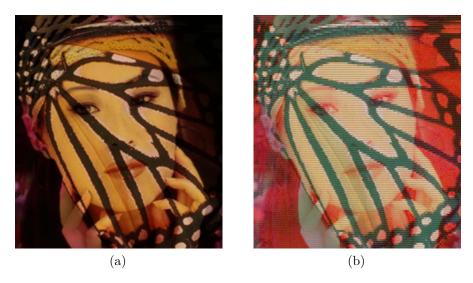

| 3.3  | Image Blending: (a) Exact and (b) ML-LVA Model with Poor Training       | 40 |

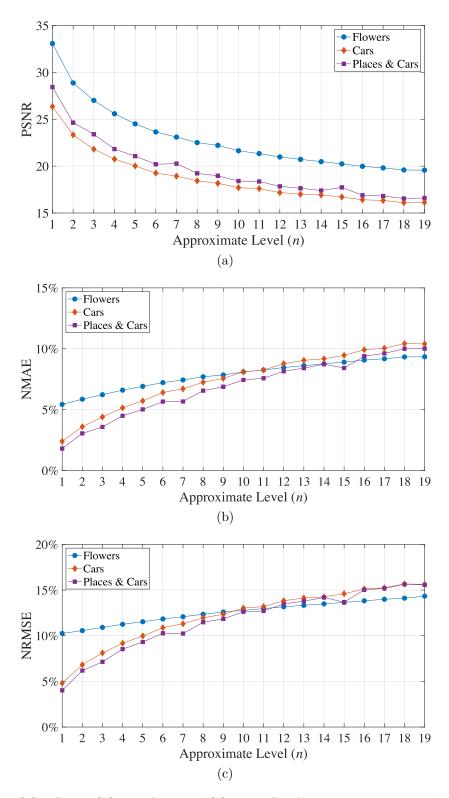

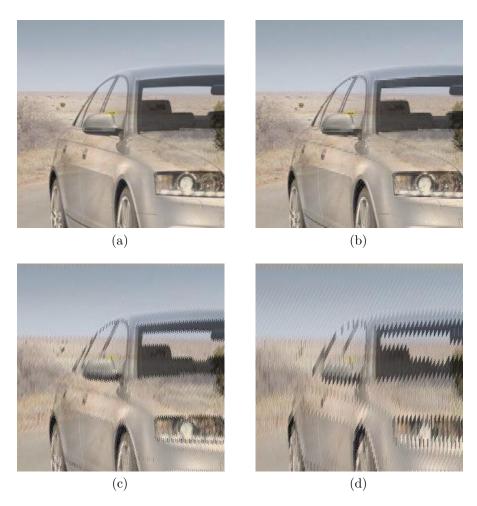

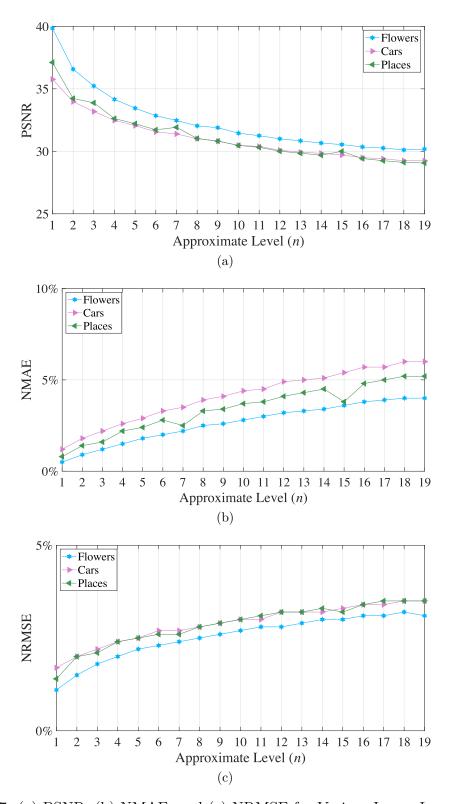

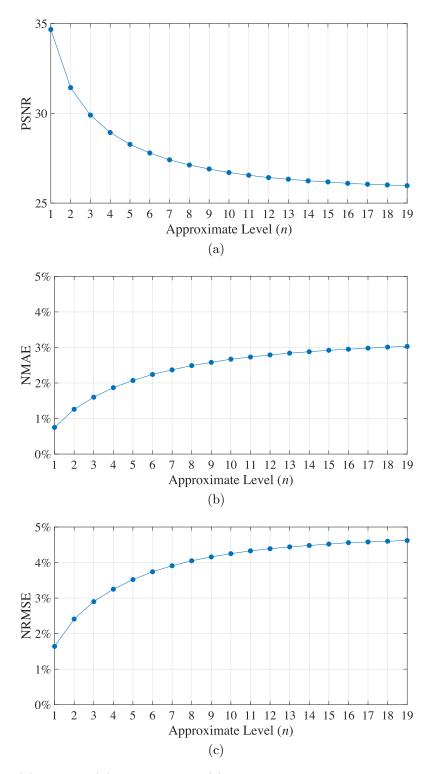

| 3.4  | (a) PSNR, (b) NMAE, and (c) NRMSE for Various Image Blending Sets       | 48 |

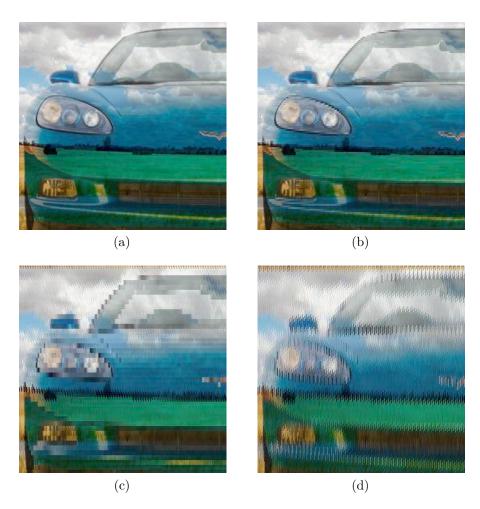

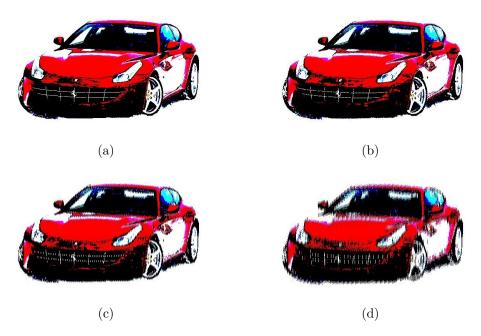

| 3.5  | Image Blending Example 1: (a) Exact, (b) $50\%$ Approximation $(n=1)$ , |    |

|      | (c) 80% Approximation (n=5), and (d) 90% Approximation (n=9)            | 49 |

| 3.6  | Image Blending Example 2: (a) Exact, (b) $50\%$ Approximation $(n=1)$ , |    |

|      | (c) 80% Approximation (n=5), and (d) 90% Approximation (n=9)            | 50 |

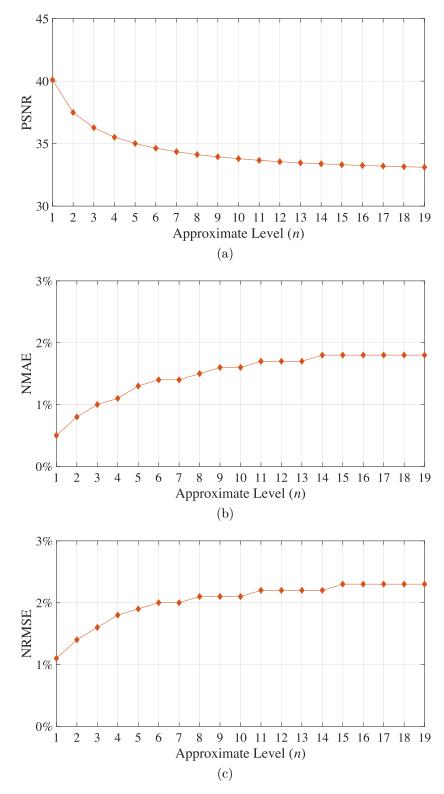

| 3.7  | (a) PSNR, (b) NMAE, and (c) NRMSE for Various Image Inversion Sets      | 52 |

| 3.8  | Image Inversion Example: (a) Exact, (b) $50\%$ Approximation $(n=1)$ ,  |    |

|      | (c) 80% Approximation (n=4), and (d) 90% Approximation (n=9)            | 53 |

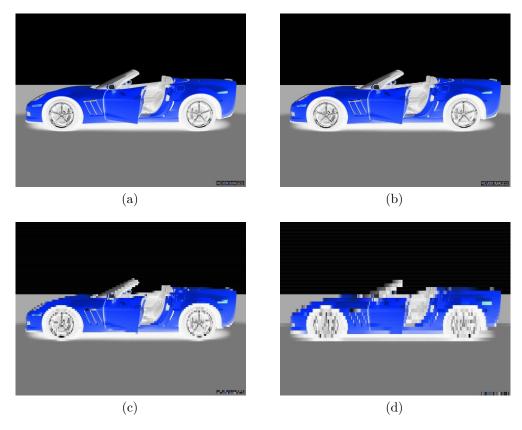

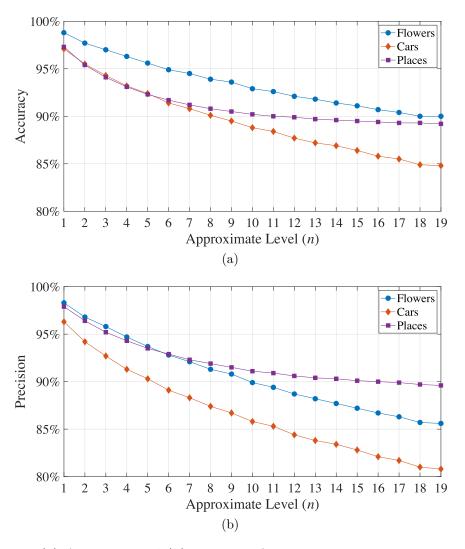

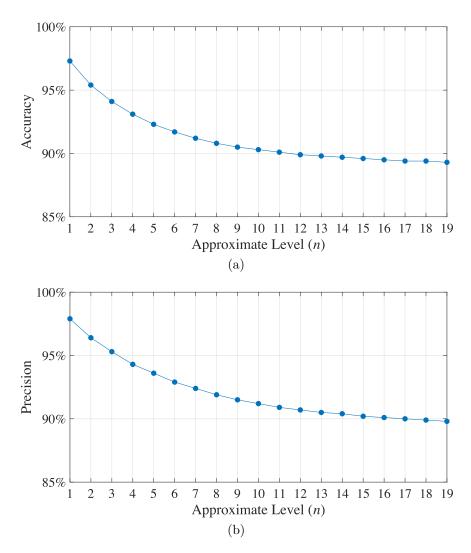

| 3.9  | (a) Accuracy, and (b) Precision for Various Image Binarization Sets .   | 54 |

| 3.10 | Image Binarization Example: (a) Exact, (b) 50% Approximation $(n=1)$ ,  |    |

|      | (c) 80% Approximation ( $n=4$ ), and (d) 90% Approximation ( $n=9$ ) .  | 55 |

| 3.11 | (a) PSNR, (b) NMAE, and (c) NRMSE for Various Approximate Levels     |     |

|------|----------------------------------------------------------------------|-----|

|      | of Audio Blending                                                    | 57  |

| 3.12 | (a) PSNR, (b) NMAE, and (c) NRMSE for Various Approximate Levels     |     |

|      | of Audio Inversion                                                   | 59  |

| 3.13 | (a) Accuracy, and (b) Precision for Various Approximate Levels Audio |     |

|      | Binarization                                                         | 61  |

| 4.1  | Methodology to Implement the Proposed LVA in Software                | 69  |

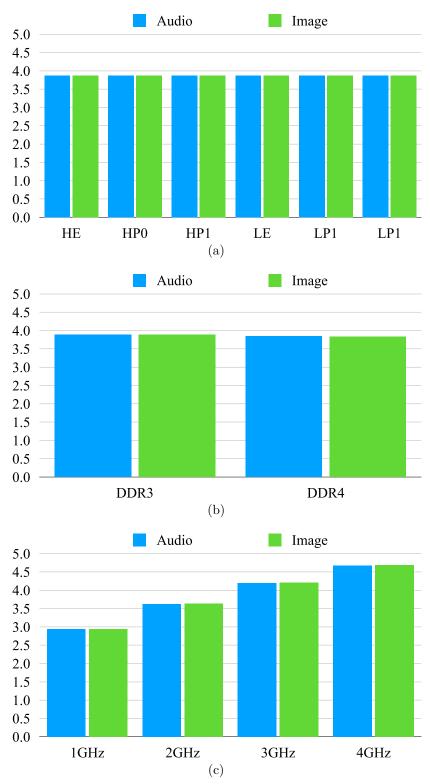

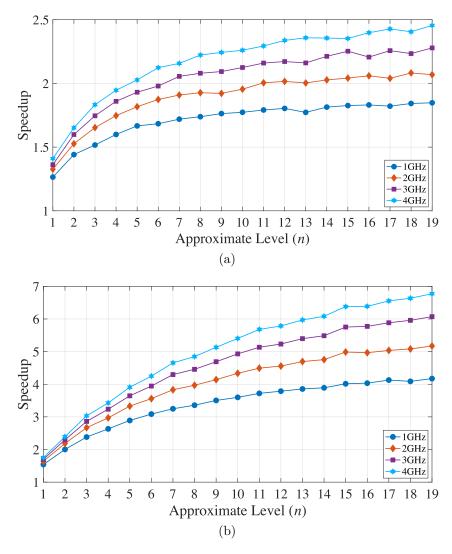

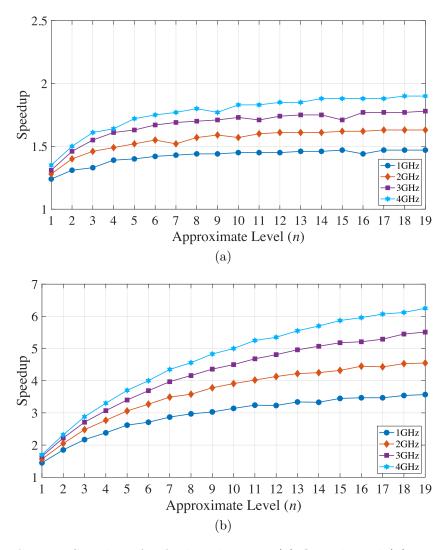

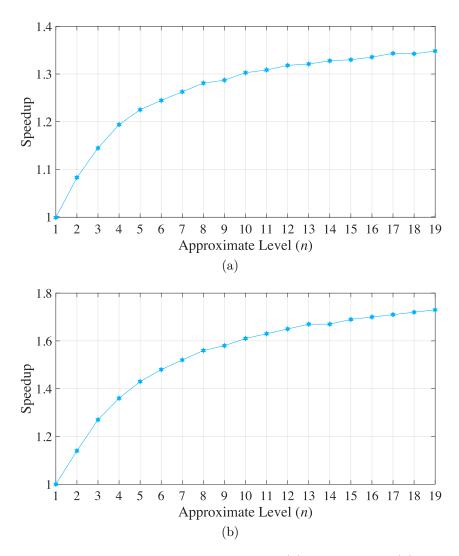

| 4.2  | Average Speedup in Memory Access when varying (a) Cache, (b) DRAM,   |     |

|      | and (c) CPU Frequency Settings                                       | 77  |

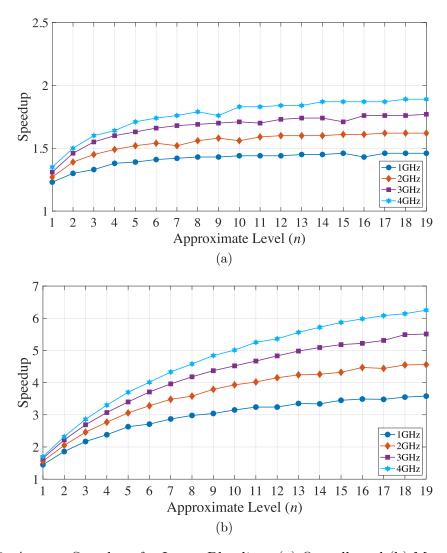

| 4.3  | Average Speedups for Image Blending: (a) Overall, and (b) Memory     |     |

|      | Loads                                                                | 81  |

| 4.4  | Average Speedups for Image Inversion: (a) Overall, and (b) Memory    |     |

|      | Loads                                                                | 84  |

| 4.5  | Average Speedups for Image Binarization: (a) Overall, and (b) Memory |     |

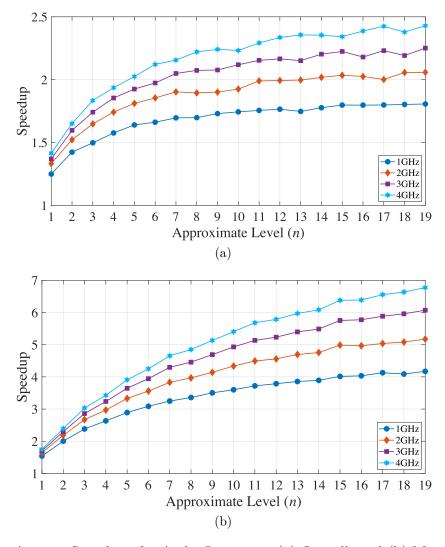

|      | Loads                                                                | 85  |

| 4.6  | Average Speedups for Audio Blending: (a) Overall, and (b) Memory     |     |

|      | Loads                                                                | 88  |

| 4.7  | Average Speedups for Audio Inversion: (a) Overall, and (b) Memory    |     |

|      | Loads                                                                | 90  |

| 4.8  | Average Speedups for Audio Binarization: (a) Overall, and (b) Memory |     |

|      | Loads                                                                | 92  |

| 5.1  | Methodology to Implement the Proposed LVA in Hardware                | 100 |

| 5.2  | Hardware Implementation Environment                                  | 104 |

| 5.3  | Architecture of the CVA6 [27]                                        | 105 |

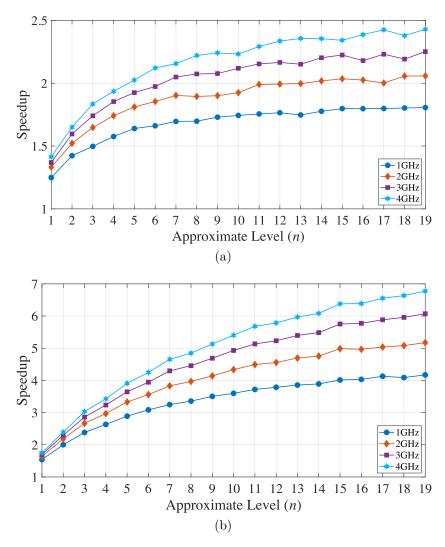

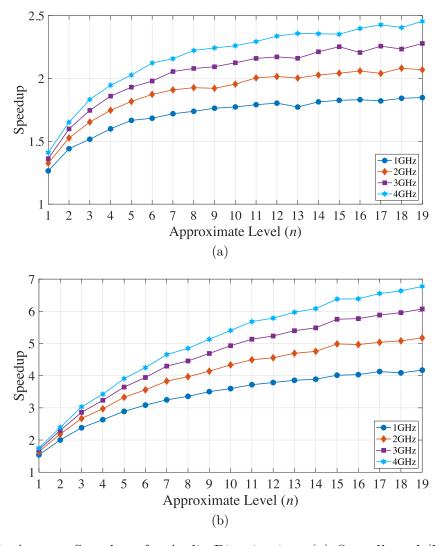

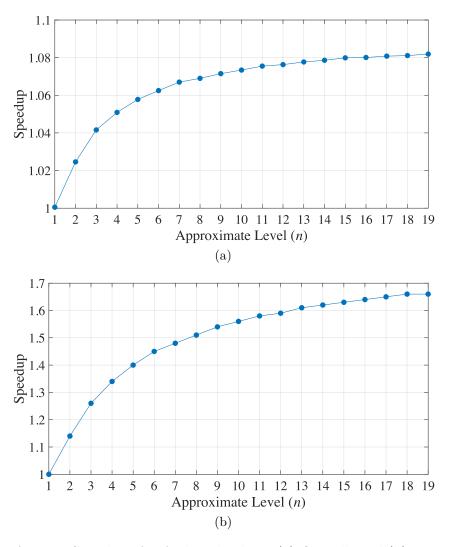

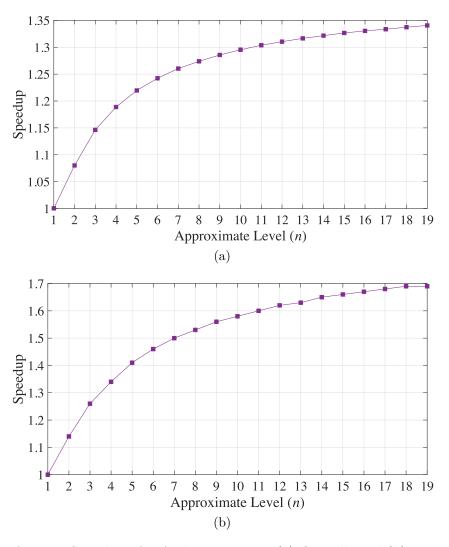

| 5.4 | Average Speedups for Image Blending: (a) Overall, and (b) Memory  |     |

|-----|-------------------------------------------------------------------|-----|

|     | Loads                                                             | 115 |

| 5.5 | Average Speedups for Image Inversion: (a) Overall, and (b) Memory |     |

|     | Loads                                                             | 116 |

| 5.6 | Average Speedups for Audio Blending: (a) Overall, and (b) Memory  |     |

|     | Loads                                                             | 118 |

| 5.7 | Average Speedups for Audio Inversion: (a) Overall, and (b) Memory |     |

|     | Loads                                                             | 120 |

# List of Tables

| 3.1 | Mapping of the Trained ML Model Developed using Images             | 43  |

|-----|--------------------------------------------------------------------|-----|

| 3.2 | Mapping of the Trained ML Model Developed using Audio Data         | 44  |

| 3.3 | Comparison of NMAE of the Proposed ML-LVA with [19]                | 62  |

| 3.4 | Comparison of NMAE of the Proposed ML-LVA with [19] when using     |     |

|     | the simlarge Dataset                                               | 63  |

| 3.5 | Comparison of NRMSE of the Proposed ML-LVA with [24]               | 64  |

| 4.1 | Cache Settings of the Intel Processor [62]                         | 74  |

| 4.2 | Cache Configurations used to Test the Proposed LVA                 | 75  |

| 4.3 | Speedup Comparison of the Proposed Software-based ML-LVA with [19] | 94  |

| 5.1 | Speedup Comparison of the Proposed Hardware-based ML-LVA with [19] | 121 |

| 5.2 | Synthesis Results of the CVA6                                      | 122 |

## List of Abbreviations

AC Approximate Computing

AMBA Advanced Microcontroller Bus Architecture

ANC Active Noise Cancellation

ASIC Application-Specific Integrated Circuit

AXI Advanced eXtensible Interface

BER Bit-Error Rate

BW Bandwidth

CAS Column Address Strobe

CPU Central Processing Unit

DDR Double Data Rate

DRAM Dynamic Random-Access Memory

ECC Error-Correcting Code

ED Error Distance

EDP Energy-Delay Product

EEPROM Electrically Erasable Programmable Read-Only Memory

FLOPS Floating Point Operations per Second

FN False Negative

FP False Positive

FPGA Field-Programmable Gate Array

GHB Global History Buffer

GPDK Cadence Generic Process Design Kit

GPU Graphics Processing Unit

HD High Definition

HPC High-Performance Computing

ID Instruction Decode

IoT Internet of Things

ISA Instruction Set Architecture

LHB Local History Buffer

LLC Last-Level Cache

LSB Least Significant Bit

LVA Load Value Approximation

LVS Load Value Speculation

MAE Mean Absolute Error

ML Machine Learning

ML-LVA Machine Learning-based Load Value Approximator

MSB Most Significant Bit

MSE Mean Squared Root

MSHR Miss Status Holding Registers

NMAE Normalized Mean Absolute Error

NRMSE Normalized Root Mean Squared Error

OCR Optical Character Recognition

PADP Power-Area-Delay Product

PARSEC Princeton Application Repository for Shared-Memory Computers

PC Program Counter

PIM Processing-in-Memory

PSNR Peak Signal-to-Noise Ratio

PULP Parallel Ultra Low Power

RAM Random-Access Memory

RED Relative Error Distance

RFVP Rollback-Free Value Prediction

RISC-V Reduced Instruction Set Computer Version 5

RM Ring Modulation

RMSE Root Mean Squared Error

ROB Reorder Buffer

ROM Read-Only Memory

SD Standard Definition

SoC System-on-Chip

SRAM Static Random-Access Memory

tCK Clock Cycle Time

TLB Translation Lookaside Buffer

TN True Negative

TP True Positive

tRCD Row to Column Delay

${

m tRP}$  Row Precharge Time

VLSI Very Large-Scale Integration

## Chapter 1

### Introduction

### 1.1 Motivation

The relentless pursuit of performance in computer architecture has always been linked to the challenge of memory latency, and the critical delay between a processor's demand for data and its eventual retrieval. This latency is not just a technical obstacle but a fundamental consequence of the von Neumann architecture [1], conceived in the mid-20th century, which tightly couples computation and memory. Early systems, such as the IBM 704 (1954), delivered a delicate equilibrium between processor speed and memory access times. However, the advent of Moore's Law in 1965 disrupted this balance, where the transistor densities began doubling roughly every 18–24 months leading to exponential gains in clock frequencies and instruction throughput. On the other hand, memory subsystems—constrained by the analog physics of charge storage and the resistive-capacitive delays of interconnects—could not keep pace. This gap in performance of memory led to slowing down computers. For instance, early processors when faced with a single cache miss or data dependency could halt the entire processor for dozens of cycles. For example, the Intel 8086's 6-stage pipeline, running at 5

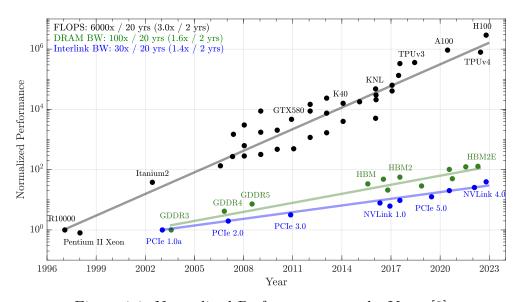

MHz, could stall for more than 20 cycles (approximately 4 μs) on a memory access miss, a stark contrast to its average instruction throughput of roughly 200 ns. By the 1990s, this growing gap had been crystallized into what Wulf and McKee famously termed the "memory wall" [2]. This gap is a result of Central Processing Unit (CPU) performance improvements that far outstripped reductions in memory latency, leaving even the most advanced processors chronically starved for data. This phenomenon of memory wall still holds in the modern days. Figure 1.1 shows the performance improvement of the computational units, i.e., processors, Dynamic Random-Access Memory (DRAM) memory and processor-memory interlink bandwidth since the mid-90s. The improvement of Floating Point Operations per Second (FLOPS) of the computations units have increased at rate of 6000× in the last 20 years compared to a much smaller 100× in DRAM Bandwidth (BW). Subsequently, we can conclude an increasingly widening gap between performance improvement of the computational units and the one of the memory.

Figure 1.1: Normalized Performance over the Years [3]

To overcome the widening gap in performance, architects have redirected their interest to advancements in microarchitecture of computers to mitigate the memory wall. For instance, out-of-order execution aims at reordering instructions on the fly to hide the latency of long instructions. Architectures such as the Intel P6 [4] and AMD's K7 [5] further advanced this concept by integrating larger Reorder Buffers (ROBs) and employing register renaming to eliminate false dependencies, namely, writeafter-read and read-after-write hazards. For instance, the AMD K7 utilized a 72entry ROB along with multiple reservation stations, enabling dynamic reordering of loads, stores, and arithmetic operations. Modern CPUs offer more than 500 ROBs, however, on Last-Level Cache (LLC) misses, the ROBs can easily get saturated causing the CPU to stall [6]. Speculative techniques [7] further extend the benefits of these microarchitectural innovations. Hardware prefetchers, such as the stridebased mechanism in AMD's Zen 3 microarchitecture [8], work to anticipate sequential memory accesses. Additionally, Machine Learning (ML) [9] driven prefetchers such as DeepPrefetcher [10], leverage ML techniques to improve prefetching. For instance, the authors of [10] used deep neural networks to predict memory access patterns more accurately. However, over-aggressive prefetching can yield to cache pollution and increased miss rates yielding to overall performance degradation [11]. In a different approach to improve memory performance, AMD's 3D V-Cache [12] demonstrated that vertically stacking cache layers can effectively increase capacity and reduce the apparent access latency.

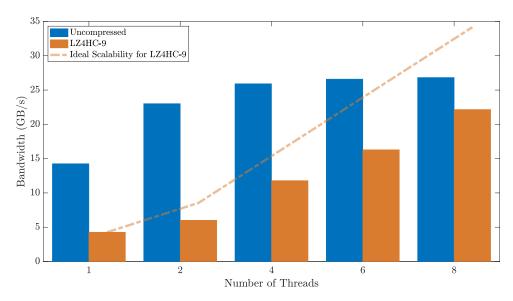

Nevertheless, even with all these advancements in microarchitecture, modern processors cannot fully address the memory wall. For instance, the developer of Blosc [13], a high performance data compressor, studied the performance improvement when the number of threads increases [13]. Figure 1.2 shows the memory bandwidth

Figure 1.2: Memory Bandwidth when Increasing the Number of Thread versus the Ideal Scalability [13]

usage when increasing the number of threads used on the Intel Xeon E3-1245 v5 4-Core processor [14]. It highlights that when using uncompressed data, the bandwidth scalability does not scale linearly, i.e., ideal scalability. Consequently, the threads do not achieve maximum throughput, resulting in idle periods caused by data starvation. On the other hand, when the data is compressed with LZ4HC-9 compressor [15], a single thread requires less bandwidth, improving scalability as more threads are used. However, when operating with eight threads, the CPU receives 35% (12GB/s) less bandwidth than expected under ideal scalability, where no memory wall exists. Thus, even software techniques that aim to complement the advanced microarchitectural techniques do not fully address the memory wall. In the face of these persistent challenges, emerging paradigms such as Processing-In-Memory (PIM) [16] have been proposed to bridge the gap between processor speed and memory performance. PIM shifts repetitive computations, e.g., multiply and accumulate operations, from the CPU to memory or its vicinity to reduce data movement [17]. Although PIM minimizes processor-memory traffic, its computational speed is hindered by the slow access time

in a Random Access Memory (RAM). This fundamental limitation makes PIM a relatively slow process. In a different approach, researchers have explored the concept of load value speculation (LVS) [7] which involves adding a unit to the processor that predicts the value to be loaded from the memory, with minimal modifications to the Von Neumann architecture. Similar to branch prediction, if the LVS is wrong, the CPU reverts to its state before the prediction and flushes the pipeline. However, all LVS techniques aim to hide memory access delays while requiring a check to the correctness of the predictions. Thus, the bandwidth usage is not reduced but rather the latency is hidden. Another disadvantage of the LVS is the costly roll-back on a wrong speculation.

In a different approach, Approximate Computing (AC) [18] has reemerged as a pragmatic technique to further improve the performance of computers. Recognizing that many modern applications can tolerate minor inaccuracies, e.g., multimedia processing, machine learning and video games, AC intentionally relaxes precision requirements in order to reduce computational overhead, lower latency, and conserve energy. AC represents a paradigm shift from traditional exact computation by deliberately introducing controlled inaccuracies to boost energy efficiency, throughput, and overall system performance. AC is tailored for applications that can tolerate small deviations without significantly affecting perceived output quality. The underlying principle is to define error margins through rigorous analysis and quality-of-service guarantees so that performance gains outweight the slight loss in accuracy. For example, the work in [19] exploits the principle of AC to relax LVS. The costly roll-back in LVS can be avoided in error-tolerant applications by accepting the wrong (approximate) value predicted. The approximate version of the LVS is commonly referred to as Load Value Approximation (LVA). A drawback of existing LVA is the hardware overhead.

e.g., lookup table, in addition to the computation needed to compute indexing/hash values used by the predictor. Additionally, the existing LVA requires continuous access to the memory in order to maintain good quality.

Given that existing methods have failed to fully address the memory wall, in this thesis we aim to address this challenge by using ML and AC. The solution we propose can be a software- or hardware-based implementation. The predictor used in the proposed LVA is static and hence reduces the overhead of operating the predictor. In the rest of this chapter, we will present the evaluation techniques of AC designs. Thereafter, we present the state-of-the-art that is most relevant to our work, followed by a discussion on the limitations of existing methods. We then introduce the proposed methodology followed by the thesis contributions and the thesis organization.

### 1.2 State-of-the-Art

Various studies in the literature have investigated methods to address memory bottlenecks. Prior to approximate computing gaining popularity in recent years, researchers have focused on exploiting the localities in order to address this challenge. In the sequel, we will restrict the discussion of related work to those methods that are most relevant to the proposed solution in this thesis. We will present the approximate memory that aims to improve memory latency and energy consumption. We will also cover the Machine Learning (ML) based prefetcher which aims to predict the subsequent load value and hence improving the hit rate in the cache. Thereafter we present Load Value Speculation (LVS), a technique that aims to predict the load value and hence hide the latency. We conclude this section with the presentation of Load Value Approximation (LVA), a technique that improves the performance of LVS by tolerating error.

#### 1.2.1 Approximate Memory

Approximate Memory consists of modifying the conventional exact memory where data can be stored approximately. For instance, the work in [20] explores an implementation of approximate DRAM. The authors of [20] propose the storage of data in a transposed fashion. Furthermore, they investigate the implementation of variable refresh rate where rows storing Least Significant Bits (LSBs) are refreshed less frequently compared to the rows storing the Most Significant Bits (MSBs). The variable refresh rate results in energy saving. In order to address the memory bottlenecks, the authors of [20] propose the load of a limited number of rows. When deploying this approach, the MSBs of multiple data elements are retrieved concurrently. Hence, more elements are retrieved faster. Furthermore, if only 16 rows out of 32 are loaded, i.e., loading the 16 MSBs and truncating the other 16 LSBs, the bandwidth would be reduced by 50%. Another approach of approximate memory in [21] proposes the compression of errortolerant data in DRAMs. Compression and decompression in distinct memory regions define varying accuracy levels, that are controlled by a software-hardware integration. While both methods present compelling strategies for leveraging approximation in memory to reduce energy consumption and improve bandwidth efficiency, they also introduce notable limitations. For instance, in [20], the use of transposed storage and variable refresh rates is applied at the region level, allowing critical data to reside in safe, fully refreshed regions. This mitigates the risk of corruption and side channel attacks in precision-sensitive applications. However, the selective loading of only MSBs and the reduced refresh of the LSB regions may still affect the data quality in regions marked as approximate, and the complexity of managing transposed access patterns and refresh schedules introduces additional hardware overhead. Additionally, the introduction of approximate regions opens potential security vulnerabilities. However, malicious code

could exploit relaxed refresh policies or compressed representations to manipulate data silently by inducing bit flips in approximate regions. Similarly, the compression-based approach in [21] imposes latency and control challenges due to the need for dynamic decompression and region management. Its reliance on software-hardware coordination for setting approximation levels requires accurate workload characterization and tight system integration, which may limit portability and scalability. Both methods would benefit from more adaptive, runtime-aware control mechanisms that can fine-tune approximation levels based on observed application behavior and quality constraints.

### 1.2.2 ML-based Prefetching

Memory prefetching is a technique that predicts and loads data into the cache before it is needed, reducing access latency and improving processor performance. The authors of [10] developed DeepPrefetcher, a method that leverages ML to enhance memory access efficiency by intelligently predicting future data requests. DeepPrefetcher harnesses deep learning to identify complex correlations within memory access sequences. By analyzing execution traces, it learns nuanced dependencies that conventional prefetchers often overlook, allowing it to anticipate future accesses more effectively. This approach involves training a deep learning model on program memory traces, capturing both short-term and long-term relationships between memory accesses. DeepPrefetcher continuously refines its predictions by updating the model with new data, adapting dynamically to evolving workloads. This adaptability makes it particularly effective in scenarios where memory access patterns are irregular, non-repetitive, or workload-dependent. By leveraging its learned understanding of execution behavior, DeepPrefetcher reduces cache misses and improves data availability, leading to enhanced overall system performance. It is especially beneficial for modern

applications with complex memory access patterns, where conventional prefetching strategies struggle to keep pace. However, a common challenge among prefetchers is their potentially incorrect predictions, which can lead to cache *pollution*, i.e., the eviction of useful data by unnecessary prefetched data, and ultimately increase miss rates [11]. As a result, prefetchers can sometimes be counterproductive, as a higher number of incorrect prefetches may degrade the performance rather than improve it. Another drawback of DeepPrefetcher is its reliance on online learning, where the model must be continuously trained in real-time to maintain accurate predictions. This process requires dedicated computational resources, leading to additional hardware overhead and increased energy consumption.

### 1.2.3 Load Value Speculation

Load Value Speculation (LVS) aims to hide the memory latency by predicting the value to be loaded. In one of the earliest work in this area, the authors of [7] introduced the idea of value locality. The authors suggest that values stored in adjacent memory addresses are comparable in magnitude. For instance, the adjacent pixels of an image stored in memory are alike in value. Subsequently, the authors present a dynamic lookup table that speculates the value of a load with the aim of hiding the memory access latency. In case of wrong speculation, the processor rolls back and flushes the pipeline. Moreover, the lookup table is updated after every memory access. This concept was widely investigated by implementing other speculation techniques such as the work in [22] and [23]. Among the common techniques used in LVS are i) last value prediction, ii) stride-based prediction, iii) context-based prediction, iv) hybrid prediction, and v) perfect confidence [23]. Last value prediction assumes that a memory load instruction will retrieve the same value as in its most recent execution. On the

other hand, stride-based prediction estimates the next load value by identifying a consistent difference (stride) between successive values of a particular load instruction. Additionally, context-based prediction relies on the past four observed values of a load instruction to determine the most likely next value. Hybrid prediction dynamically selects the most accurate predictor between context-based and stride-based methods. Finally, perfect confidence utilizes the hybrid predictor but only applies the predicted value when it is certain to be correct, simulating an ideal confidence mechanism.

All LVS techniques access the memory to confirm the correctness of the speculation and roll-back in case of wrong speculation.

#### 1.2.4 Load Value Approximation

Since roll-backs in LVS are expensive in terms of hardware requirement and loss in clock cycles, some researchers have proposed the idea of Load Value Approximation (LVA). These techniques speculate a value without a roll-back in case of a wrong prediction which results in approximation. For instance, the work in [19] proposed a load value approximation which relies on a dynamic predictor. The accuracy of the predictor can be improved by providing the value of the recent loads, which saves in bandwidth and energy for a cost in quality. The authors of [19] use a predictor with a Global History Buffer (GHB) to record recent load values and an approximator table indexed by a hash derived from the GHB along with the load instruction address to generate an estimated value on a cache miss. Additionally, the predictor includes a Local History Buffer (LHB), which records the sequence of recent values following patterns detected in the Global History Buffer (GHB). The approximator then estimates a value by averaging entries in the LHB, and thus allowing the processor to continue execution while the actual value is fetched in the background to train the predictor future

estimations. Unlike traditional value predictors that require an exact match and trigger rollbacks if even a slight discrepancy occurs, this approach uses a relaxed confidence window to tolerate minor differences, thereby eliminating rollbacks and enhancing energy efficiency. Furthermore, the design incorporates an approximation degree, which determines how many subsequent load misses can reuse the same predicted value before the actual data is fetched for retraining, thus effectively balancing accuracy with reduced memory fetches even when value delays occur. Although the LVA proposed in [19] introduces a solution that aims to address the memory wall, however it has the drawback of using a complex hardware to predict the load value. For instance the work in [19] requires the calculation of complex indexes and keeping track of LHB and GHB. Furthermore, it uses a dynamic predictor that requires a continuous memory access to maintain an acceptable low quality.

Rollback-Free Value Prediction (RFVP) [24] is an LVA technique designed for Graphics Processing Units (GPUs). RFVP reduces memory latency by predicting values for cache misses and selectively discarding some predictions. When a load is not discarded, the actual value retrieved from the memory updates the predictor used in the RFVP, improving its accuracy. The predictor relies on a value history table indexed using a hash derived from the program counter of the load instruction. Each entry stores three key elements, namely, the most recent value loaded from memory and two stride values that capture how the load value has changed over time. RFVP predicts a new load value by adding the last loaded value to one of the observed strides. To enhance stability, the predictor updates the stride entry only when the new stride is consistent with past patterns. Because GPU threads within a warp may not execute simultaneously, some threads can be inactive during a cache miss but may later request the same data. RFVP anticipates these accesses by precomputing

predictions for inactive threads, ensuring they receive meaningful approximations rather than outdated or random values. This approach maintains consistency and prevents errors due to unpredictable data. Similar to the LVA proposed in [19], RFVP uses of a dynamic predictor that updates through memory access to sustain an acceptable output quality. Furthermore, the RFVP predictor has a computation overhead, e.g., computation of a hash index, to approximate the load value while also requiring a lookup table that uses a complex updating method.

### 1.3 Problem Statement

Researchers have long investigated options to improve the performance of computers, e.g., out-of-order execution. However, most modern computers face a significant challenge in gaining speedup due to the memory wall. A limited number of researchers have explored approximation or prediction-based solutions to address memory bottlenecks. The most prominent techniques in approximating the load value are the work in [19, 24]. Existing LVA techniques rely heavily on memory access to update the predictor and hence maintain an acceptable quality. Moreover, existing methods of LVA require complex hardware that has substantial resource usage and/or require the computation of values needed to index/guide the predictor.

Alternatively, some researchers have shifted their focus towards exploring approximate memory to address the memory wall, e.g., the work in [20]. However, the approximate memory could potentially disrupt the functionality of the error correction code (ECC) in the memory. Additionally, an approximate memory has an increased complexity of the memory controller, which could yield in a significant overhead and a delay.

Given these limitations, we believe that an approach approach with minimal

overhead is better suited to achieve meaningful speedups while preserving a small hardware footprint. A key enabler for this is the use of a static predictor, which would avoid the need for continuous updates and complex runtime mechanisms. A statically designed model significantly reduces implementation complexity and allows for faster predictions, thereby decreasing latency and energy consumption. With the recent progress in ML algorithms and the increasing availability of high-performance computation resources, ML-based LVA solutions would offer a compelling alternative. Lightweight ML models, such as small neural networks or decision trees, can be trained offline to learn patterns in memory load value, enabling accurate approximations that do not require dynamic adaptation or rollbacks.

An advanced ML model can be trained once using representative workloads and a statically trained predictor used solely for runtime prediction that operates efficiently during execution. This approach eliminates the need for re-training at runtime and ensures consistent prediction performance. Such models can generalize across various applications, offering broader adaptability than traditional heuristic-based predictors. However, ML models are inherently resource-intensive, often requiring significant memory and computation. If not carefully designed, their demands can further burden the already strained memory system, thereby worsening the memory wall problem. To fully realize the benefits of ML in this context, it is essential to develop compact, statically trained models tailored for hardware efficiency, enabling low-overhead with minimal performance trade-offs.

### 1.4 Proposed Methodology

The objective of this thesis is to address the memory wall by using Machine Learning (ML) and Approximate Computing (AC). We argue that this challenge can

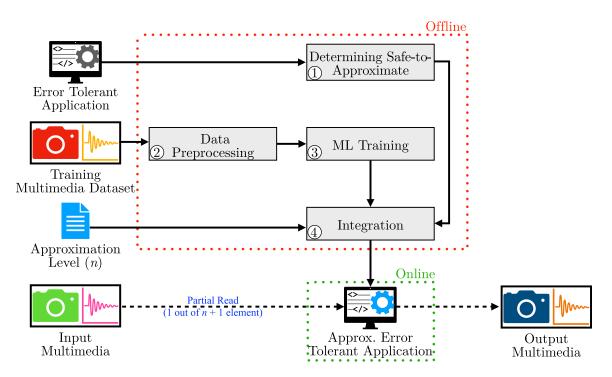

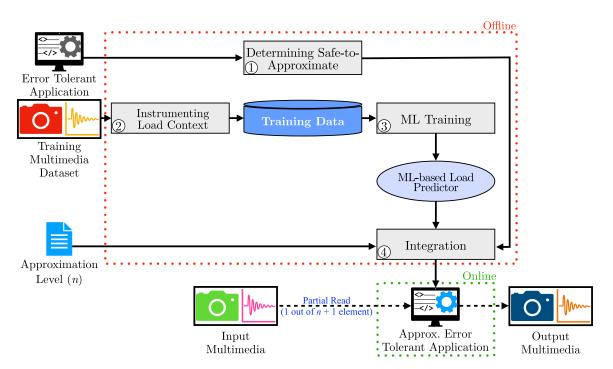

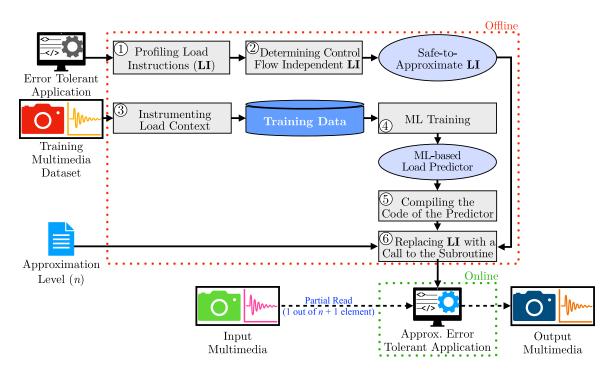

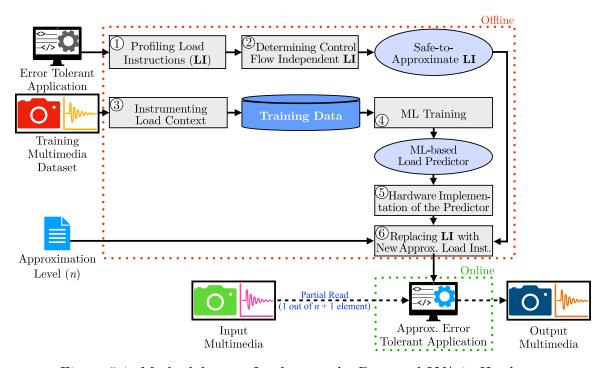

be addressed with a solution that satisfies three key criteria: i) improve performance, ii) maintain an acceptable quality, and iii) efficient usage of resources. Towards this goal, an ML model is trained to learn the patterns in the load values while recognizing that perfect accuracy is unfeasible. Thereafter, the trained ML model is used to predict the load value. Given the inherent inaccuracy of ML models, we accept the predicted value as-is resulting in an approximately computed load value. Subsequently, the ML model is trained to achieve a controlled quality that is deemed acceptable. We propose to develop a static predictor, where the ML model undergoes a single training phase and then is reused indefinitely. The proposed ML-based Load Value Approximator (ML-LVA) can be integrated into existing off-the-shelf hardware through a software implementation, or implemented as a dedicated unit in newly designed hardware. The proposed ML-LVA can be applied to any domain in which the principle of value locality holds. In this thesis, we focus on its implementation in multimedia applications, as these applications naturally exhibit value locality. For example, in an image, a given pixel typically has neighboring pixels with similar values. Subsequently, the proposed model in this thesis can be deployed in video games, augmented and virtual reality systems where performance is a key necessity while a slight loss due to approximation is tolerable. The details of the proposed methodology for developing and using a ML-LVA are depicted in Figure 1.3. The methodology consists of Offline and Online phases. The Offline phase is used to build the LVA predictor, while the Online phase represents the application's execution stage. The Offline phase requires three inputs: i) an Error Tolerant Application, ii) a Training Multimedia Dataset, and iii) an Approximation Level (n). Using these three inputs, the Offline stage produces an approximated error tolerant application as an output, which will be used by the Online phase to generate as an output the approximated multimedia

Figure 1.3: Methodology of the Proposed ML-LVA

result. The Offline phase consists of four main steps. In Step ① the error tolerant application is profiled to determine the "safe-to-approximate" load instructions. This is a critical step in the process since approximating load values that do not tolerate error could lead to catastrophic scenarios. For instance, loading a loop boundary or memory addresses cannot be approximated. On the other hand, loading multimedia data, e.g., pixel of an image, is error-tolerant and thus can be determined as "safe-to-approximate". The identification of safe-to-approximate load instructions can be performed at either the high-level programming or low-level (assembly) code. For applications written in a high-level language, the programming language must provide a mechanism to explicitly declare variables as safe-to-approximate, and the compiler must be extended to recognize these declarations and generate the corresponding approximations. Alternatively, when the application is provided as assembly code, the analysis can be performed directly at the instruction level. Although in this thesis

the identification of safe-to-approximate load instructions is performed manually, this process could be automated in the future using, for example, some machine learning technique, which can evaluate the impact of approximation and automatically determine the safe-to-approximate instructions. In parallel, in Step ② we perform a data preprocessing on the training multimedia dataset. This step is crucial as raw data cannot be fed to an ML model to perform training. Additionally, in this step, we split the data into training and testing data in order to validate the quality of the ML model. Thereafter, we perform the ML training in Step ③. The trained model will serve as the load value predictor, i.e., the ML-LVA. In Step ④, we integrate the ML-LVA into the error-tolerant application, where a portion of the safe-to-approximate load instructions is replaced. The ratio of replacement is defined by the approximation level (n), meaning that we retain 1 out of n+1 instructions as exact while the others are approximated. Every approximated instruction becomes a call to a subroutine, invoking a custom instruction that can be implemented in software or in hardware.

In the software-based approach, this custom instruction is realized as a conventional function call to a software routine that performs load value prediction using the trained ML model. This solution is intended for deployment in existing off-the-shelf hardware platforms, where hardware modifications are either impractical or impossible. As such, it enables the integration of approximate load value prediction without requiring architectural changes. To evaluate this method, the software-based implementation of the ML-LVA was deployed in GEM5 [25], simulating an x86-based architecture. In this evaluation, the "Timing Simple CPU" [26] was used, and various CPU frequencies, cache settings and DRAM configurations were tested to assess the impact of the memory hierarchy on performance gains. In contrast, in the hardware-based implementation, the custom instruction is backed by a dedicated hardware accelerator that executes the

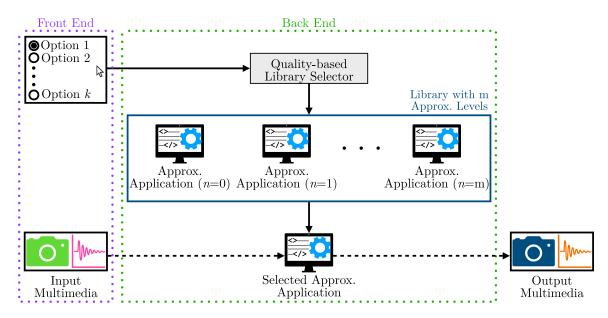

Figure 1.4: Deployment Framework for the Proposed Methodology

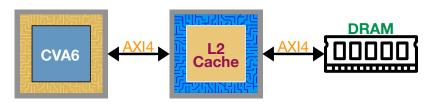

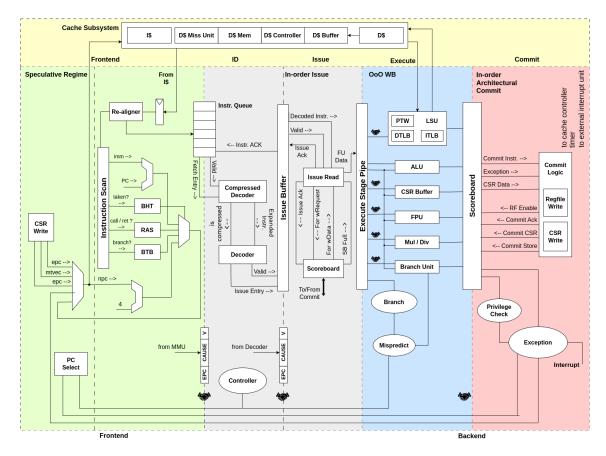

ML prediction logic directly in silicon. This accelerator acts as a coprocessor integrated into a newly designed processor pipeline. In this thesis, the hardware ML-LVA was implemented within the CVA6 design [27], a RISC-V processor [28], extending its instruction set architecture (ISA) to include a custom opcode. When the approximated instruction is encountered during execution, it triggers the custom instruction, which routes the request to the ML-LVA accelerator. This tightly coupled design eliminates software overhead and significantly reduces latency, making it suitable for high-performance systems where hardware design flexibility is available. By supporting both software and hardware realizations, the ML-LVA framework offers flexibility for deployment across a wide spectrum of systems—from commodity platforms to next-generation processor designs. In both the software and hardware implementations, we investigate the ML-LVA framework for 8-bit applications. Nonetheless, certain design choices have been made to ensure that the methodology can scale effectively to larger designs, such as 16-bit or 32-bit applications.

The proposed methodology can be deployed by a user as shown in Figure 1.4. First,

the back end developer creates multiple versions of the same approximated application with each version corresponding to a specific approximate level (n). Subsequently, in the front end, the user selects the desired quality from an option menu, similar to how a user selects video quality, such as Standard Definition (SD), High Definition (HD), or 4K, in a streaming service. Additionally, the user provides the input multimedia to the application. A selector function in the back end then picks the application variant from the library that best matches the user's chosen quality level. For instance, the user might select SD to prioritize performance at the cost of reduced output quality. Internally, the developer maps this SD setting to, for example, an approximation level of 4, i.e., n=4, which corresponds to an 80% approximation. Finally, the selected application processes the input multimedia to produce the output. The deployment, shown in Figure 1.4, could be further improved by compiling a single version of the application into an executable file -commonly referred to as the binary or binary codeand then passing the approximate level (n) dynamically. For example, instead of compiling a separate binary for each approximation level, a single application binary code can be compiled to accept the approximation level (n) as a runtime argument. This value can be passed via the argument vector, i.e., argv, when launching the application. At runtime, the program retrieves this argument to determine how aggressively to approximate. The mechanism for accessing the argument may vary depending on the underlying architecture. For instance, on x86 it may be fetched from the stack, while on RISC-V it may be accessed through a register.

To validate the quality and effectiveness of the proposed ML-LVA methodology we evaluate it using a diverse set of multimedia applications. These include image processing, i.e., image blending, image inversion, and image binarization, as well as audio processing tasks such as audio blending, audio inversion, and audio binarization.

These applications were selected due to their error-tolerant nature and their dependence on memory-intensive operations, making them ideal benchmarks for assessing the impact of approximate load value prediction. Experimental results indicate that the trained ML-LVA was able to achieve a quality that outperforms state-of-the-art. Similarly, both the software- and hardware-based implementations of proposed ML-LVA outperform existing LVA techniques where substantial speedups both application overall as well as in memory loads were measured.

## 1.5 Thesis Contributions

The main contribution of this thesis is overcoming the memory wall by leveraging Machine Learning (ML) and Approximate Computing (AC) for memory load value approximation. The proposed methodology addresses this challenge by reducing the memory bandwidth needed by a given application and approximating (predicting) the values that were not loaded from the memory. The predictor used in thesis is generated by training an ML model. The key contributions of this work are outlined below, with references to relevant publications included in the Biography section at the end of the thesis:

• A methodology for machine learning-based load value approximator (ML-LVA) which presents a complete design and deployment framework that includes identifying "safe-to-approximate" load instructions, performing offline training of an ML model to predict these values, and integrating the predictor into error-tolerant applications. The output quality is controlled via a tunable approximation level. The methodology supports both software- and hardware-based realizations and enables quality-performance trade-offs through user-configurable settings [Bio-Cf4].

- A static machine learning model that predicts unfetched memory load values to reduce access latency. By adopting a static approach, the proposed ML-LVA eliminates the deployment overhead of a dynamic predictor. The proposed ML-LVA consistently produced high-quality results across six multimedia applications, with output errors typically below 10%. In some cases, the output was indistinguishable from the original. For classification based-applications, accuracy and precision exceeded 98% at 50% approximation and remained above 80% even at 95% approximation [Bio-Cf1, Bio-Cf5].

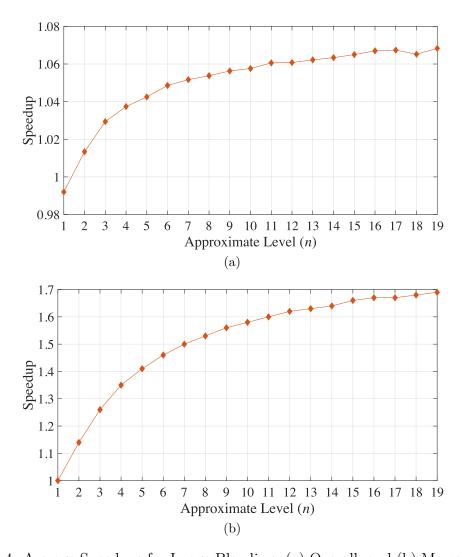

- A software-based implementation of the proposed methodology deploying the ML-LVA as a callable subroutine on commercial hardware. Safe-to-approximate load instructions are replaced with subroutine calls to enable approximate execution via the trained ML model. We evaluate this solution on six diverse multimedia applications using the GEM5 simulator configured for an x86 architecture. The implementation delivered overall application speedups of up to 1.23×, and more than 6× faster value loading in multiple cases [Bio-Jr1].

- A hardware-based implementation integrating the ML-LVA predictor as an accelerator within the CVA6 RISC-V processor [27] using a custom instruction. Implemented in the form of a lightweight ROM, this design enables fast, low-overhead inference without complex logic operations. We evaluate this approach on four multimedia applications, achieving overall speedups up to 1.21× and memory load gains of 1.47×. Synthesis results show that incorporating ML-LVA into CVA6 incurs modest overheads: area increases by 5.09% and power consumption rises by only 0.79% [Bio-Jr3].

## 1.6 Thesis Organization

The rest of this thesis is organized as follows: in Chapter 2, we introduce the preliminary notions needed to ease the understanding the remainder of this thesis. This chapter focuses on defining the key evaluation metrics used throughout the work, including quality metrics for assessing the effectiveness of the ML-LVA, and performance metrics for analyzing its impact on resource usage. Additionally, we present the mathematical background underlying the target applications, along with an explanation of how the ML-LVA influences their behavior.

In Chapter 3, we present the dataset used along with the training process and the quality of the proposed ML-LVA. We also provide the details of the input needed by the ML-LVA to predict the load value along with the prediction method. Furthermore, we evaluate the quality of the ML-LVA when simulated in audio and image blending applications. Thus, in Chapter 3 we will expand and present Steps ② and ③ of the proposed methodology shown in Figure 1.3.

In Chapter 4, we present Steps ① and ④ of the proposed methodology, namely, the software-based implementation of the proposed ML-LVA. We present in details how we determine a safe-to-approximate instructions. Furthermore, we expand the work in Step ④ by outlining the process of transforming the ML model into an optimized software solution. Furthermore, we present the measuring environment used to evaluate the efficiency of the software-based implementation which consists of simulating an x86 processor in GEM5 with various cache and DRAM configurations. Thereafter, we present the speedup achieved in memory access operations as well as the application when the software-based implementation is deployed. The performance analysis was performed using six multimedia applications, namely, image blending, image inversion, image binarization, audio blending, audio inversion and audio binarization.

Chapter 5 describes how Step ④ of the proposed methodology shown in Figure 1.3 can be adopted for a hardware-based implementation. In this chapter, we present the RISC-V CPU used and the modifications performed in order to integrate the ML-LVA. We present the custom assembly instructions that were added to the Instruction Set Architecture (ISA) permitting the usage of the ML-LVA. Furthermore, we evaluate the benefits of these new instructions in terms of speedup in memory access and application performance using multimedia applications. We provide experimental results on multimedia applications, including image blending, image inversion, audio blending and audio inversion.

We conclude this thesis in Chapter 6, where we provide closing remarks and future directions.

# Chapter 2

# Preliminary

## 2.1 Introduction

This chapter describes the metrics used to evaluate the proposed Load Value Approximation (LVA) techniques. Rather than presenting empirical results, the chapter focuses on defining the evaluation methodology and contextualizing the approximation within practical application domains. The aim is to lay the foundation for the detailed analysis that follows in the subsequent chapters.

We first introduce the mathematical formulations of the metrics used to assess the impact of LVA. These include measures related to performance, accuracy, and resource efficiency. By formalizing these concepts, the section ensures a consistent and precise basis for analyzing the effectiveness of the proposed LVA across various implementation contexts, whether hardware or software. We then present the six multimedia applications selected as representative case studies for applying LVA. This chapter describes the structure of each application and highlights the specific mathematical operations that are suitable candidates for approximation. Understanding the underlying operations permits the reader to understand how they

tolerate imprecision and how their approximation can be leveraged by the ML-LVA to enhance performance. Together, these preliminaries provide the necessary background for interpreting the evaluation results presented in later chapters.

# 2.2 Evaluating Approximate Computing

The proposed ML-LVA relies on Approximate Computing (AC). Therefore, it is important to understand the assessment methods used to identify the quality and gains of an AC design. In this section, we will delve into the evaluating techniques of AC.

The usability of an AC design can be determined if the delivered quality falls within an acceptable range of tolerable error. The generated quality of an AC design can be measured using different metrics that can broadly be classified into two categories: i) arithmetic error metrics that quantify the numerical deviation, and ii) classification metrics that assess correctness in binary decisions. Some of these metrics include [29]:

• Error Distance (ED) is the arithmetic distance between the exact value  $(E_v)$  and the approximate value  $(A_v)$  by a given set of inputs. Hence the ED can be written as:

$$ED = E_v - A_v \tag{1}$$

• Relative Error Distance (RED) is the ratio of the relative ED with respect to the exact value  $(E_v)$ :

$$RED = \frac{ED}{E_v} \tag{2}$$

• Mean Absolute Error (MAE) is the average of the absolute values of all ED in space, i.e., n number of instances:

$$MAE = \left(\frac{\sum |ED|}{n}\right) \tag{3}$$

• Normalized Mean Absolute Error (NMAE) is measured to have a better analysis for the worst-case scenario error. NMAE is normalized using  $ED_{max}$ , the maximum ED in space, e.g.,  $ED_{max} = 255$  for 8-bit applications, and computed as:

$$NMAE = \frac{MAE}{ED_{max}} \tag{4}$$

• Mean Squared Error (MSE) is the average of the ED squared:

$$MSE = \frac{\sum ED^2}{n} \tag{5}$$

• Root Mean Squared Error (RMSE) is the square root of MSE:

$$RMSE = \sqrt{MSE} \tag{6}$$

Normalized Root Mean Squared Error (NRMSE) is computed in a similar fashion to NMAE:

$$NRMSE = \frac{RMSE}{ED_{max}} \tag{7}$$

• Peak Signal-to-Noise Ratio (PSNR) evaluates the quality of an image or video by comparing the original signal to the noise introduced by the new design. For 8-bit applications, the PSNR is computed as [30]:

$$PSNR = 20 \log_{10} \left( \frac{255}{RMSE} \right) \tag{8}$$

• Bit-Error Rate (BER) is the percentage of faulty bits in the output. The BER is different from all previously discussed error metrics since it disregards the arithmetic error. The BER can be expressed in terms of False Negative (FN),

False Positive (FP), True Negative (TN) and True Positive (TP) as:

$$BER = \frac{FN + FP}{FN + FP + TN + TP} \tag{9}$$

• Accuracy is the overall proportion of correct predictions made out of all predictions. Similar to BER, the accuracy also does not measure arithmetic error. Accuracy can be computed as:

$$Accuracy = 1 - BER = \frac{TN + TP}{FN + FP + TN + TP}$$

(10)

Precision is the fraction of predicted positive instances that are indeed correct, emphasizing the accuracy in making positive predictions. Similar to BER and the accuracy metrics, precision does not measure arithmetic error. Precision is computed as:

$$Precision = \frac{TP}{TP + FP} \tag{11}$$

The selection criterion of the error metric is driven by the type of application. For instance, in a system that generates a true or false response, the classification metrics are the suitable ones.

In addition to error metrics, physical design metrics are essential when evaluating the practicality and efficiency of an AC design. These metrics capture the tangible costs of implementing a design in hardware and are typically expressed in terms of area (A), delay (D), and power (P). While an approximate design may tolerate some degradation in output quality, it must still offer meaningful gains in one or more physical dimensions, otherwise, the trade-off is unjustified.

To assess the overall hardware efficiency and compare different designs fairly,

composite metrics are often employed. These metrics combine multiple resource constraints into a single value, helping designers analyze trade-offs and identify optimal points along the performance-cost spectrum [31]:

• Power-Area-Delay Product (PADP): This metric captures the overall hardware cost by multiplying the three primary physical factors. It is particularly useful when all three resources—power (P), area (A), and delay (D)—are equally important in the target application.

$$PADP = P \times A \times D \tag{12}$$

• Energy-Delay Product (EDP): This metric evaluates the trade-off between energy consumption (E) and performance. It is especially relevant in battery-powered and energy-sensitive systems, where reducing both energy and execution time is critical. Since energy is the product of power and time (E = P × D), EDP can be rewritten as:

$$EDP = E \times D = P \times D^2 \tag{13}$$

The choice between PADP, EDP, or other derived metrics often depends on the specific goals and constraints of the system being designed. For instance, in mobile and embedded devices, minimizing energy and latency is often prioritized, making EDP a suitable metric. In contrast, for high-performance computing systems where throughput is more critical, delay (execution time) or PADP might be emphasized more. Moreover, when approximation is applied at the software level, execution time becomes an even more significant factor. Faster execution not only improves

responsiveness but can also indirectly reduce total energy consumption, especially in systems where power scales with utilization. Therefore, speedup, defined as the ratio of execution time between the exact and approximate versions, is a key metric in these contexts. It provides a direct measure of how much computational efficiency is gained through approximation.

Ultimately, the effectiveness of an AC design must be evaluated in terms of both quality loss using error metrics and resource savings by analyzing the physical metrics. A good approximation strikes the right balance between these two aspects, delivering meaningful hardware and performance benefits while keeping the output within acceptable quality bounds.

# 2.3 Multimedia Applications

To evaluate the applicability of LVA in practical scenarios, six multimedia applications have been selected as representative case studies in this thesis. These applications span both image and audio processing tasks, relying on simple yet computationally relevant operations. Each is well-suited to approximate computing due to the inherent error tolerance in human perception. Multimedia workloads often tolerate minor deviations in data values without significantly degrading the perceived quality of the output, making them ideal for exploring trade-offs between performance and accuracy. Moreover, multimedia applications frequently process large volumes of data in parallel, which amplifies the performance benefits of techniques like LVA that reduce memory latency and computational effort. By covering a diverse set of operations—ranging from arithmetic-heavy blending to memory-bound thresholding and inversion—this selection offers a comprehensive and realistic benchmark for assessing the effectiveness

of LVA in real-world, error-resilient domains. In the sequel, we outline the applications and their corresponding mathematical operations. The multimedia applications used in this thesis are:

### 1. Image Blending [32]

Image blending combines two images by multiplying their corresponding pixel values, optionally scaled by a blending factor. This operation is common in graphics design and visual effects. For example, for 8-bit images, the blending operation is defined as:

$$I_{\text{blend}}(x,y) = \alpha \cdot \sqrt{I_1(x,y) \cdot I_2(x,y)}$$

(14)

where  $I_1$  and  $I_2$  are the input images, (x, y) denotes the spatial coordinates of a pixel in the image, and  $\alpha \in [0, 1]$  is a blending coefficient. The square root operation ensures that the resulting values remain within the 8-bit range. Since this operation requires the calculation of the square root –a computation intensive operation– the overall speedup in the application is expected to be significantly less compared to the one in the memory access since a smaller portion is spent on the memory load.

### 2. Ring Modulation (Audio Blending) [33]

Ring modulation blends two audio signals by pointwise multiplication of their 8-bit unsigned sample values that ranges from 0 to 255. The formula for this operation, similar to image blending, is:

$$s_{\text{mod}}(t) = \alpha \cdot \sqrt{s_1(t) \cdot s_2(t)} \tag{15}$$

where  $s_1$  and  $s_2$  are the two audio streams, t denotes the discrete time index, and  $\alpha$  is the scaling factor applied to control the intensity of the effect. Similar to image blending, this operation involves two back-to-back loads, one for each audio signal. The approximation could help accelerate the processing of long audio signals by reducing the cost of these loads, leading to a reduced execution time. However, similar to the image blending, as the operation includes the calculation of the square root, the speedup achieved in the application due to the LVA is expected to be significantly less than the one observed in the memory access.

### 3. Image Thresholding (Image Binarization) [34]

Image thresholding simplifies a grayscale image by converting it to a binary image using a fixed intensity threshold:

$$I_{\text{thresh}}(x,y) = \begin{cases} 255, & I(x,y) > T \\ 0, & I(x,y) \le T \end{cases}$$

$$\tag{16}$$

where I is the input image, (x, y) denotes the spatial coordinates of a pixel in the image, and T is the selected threshold. This operation only requires a single load per sample followed by a simple comparison, making it more dependent on memory access compared to image blending or ring modulation. Thus, while approximating, a higher speedup in the memory access will have a higher impact on the performance improvement observed at the application level.

### 4. Infinite Clipping (Audio Binarization) [35]

Infinite clipping transforms an audio signal by reducing each sample to a binary representation of its polarity. Given that the samples are 8-bit unsigned, they are first centered around zero. The operation is defined as:

$$s_{\text{clip}}(t) = \begin{cases} 255, & s(t) > T \\ 0, & s(t) \le T \end{cases}$$

$$(17)$$

where s is the audio stream t denotes the discrete time index, and T is the threshold. The resulting values are either 0 or 255, depending on the comparison. Similar to image thresholding, this operation involves a single load and simple computation. Thus, the benefit of the LVA reverberates more at the application level.

### 5. Image Negatives (Image Inversion) [36]

Image negatives transform an image into its negative by subtracting each pixel value from the maximum intensity:

$$I_{\text{neg}}(x,y) = 255 - I(x,y)$$

(18)

where I is the input image, and (x,y) denotes the spatial coordinates of a pixel in the image. This operation is visually intuitive and widely employed in photographic effects and preprocessing. Its reliance on a straightforward subtraction operation makes it another potential candidate to test the proposed LVA. Similar to thresholding, image negatives involve a single load followed by a straightforward subtraction. Consequently, the potential speedup from LVA is higher, contributing to a larger reduction in the overall execution time, i.e., higher speedup.

### 6. Audio Polarity Inversion [37]

Polarity inversion flips the audio waveform around its midpoint. In the 8-bit unsigned format, this is implemented by inverting the sample around 128:

$$s_{\text{inv}}(t) = 255 - s(t)$$

(19)

where s is the audio stream and t denotes the discrete time index. This operation generates an inverted waveform, which is perceptually indistinguishable in numerous playback environments, rendering it suitable for evaluating approximation in subtraction or data loading. Similar to image inversion, polarity inversion entails a single load and a straightforward subtraction. Consequently, the speedup observed at the application level will be substantial.

In this thesis, specific parameters were set for each application to align with practical use cases. For instance, for the blending tasks, the blending factor  $\alpha$  was set to 1, reflecting typical settings in image editing [32] and audio mixing tools [38]. For image thresholding, the threshold was selected using Otsu's method [39], a standard approach in optical character recognition (OCR) to eliminate noise in scanned images [40]. Simple inversion operations, such as image negatives and polarity inversion, also benefit significantly from LVA due to their minimal arithmetic requirements and single-load nature. In particular, audio polarity inversion is commonly used in active noise cancellation (ANC) systems, where inverting the polarity of noise allows it to destructively interfere with the original signal, thus canceling it out [41].