# **Design and Demonstration of Optical Logic Gates with Electronic Interface for Optical Switching Applications**

#### Ataollah Mahsafar

**A Thesis**

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of

Master of Applied Science (Electrical Engineering) at

Concordia University

Montréal, Québec, Canada

September 2025

© Ataollah Mahsafar, 2025

#### CONCORDIA UNIVERSITY

#### School of Graduate Studies

| This is to certify th | nat the thesis prepared                                                           |                          |

|-----------------------|-----------------------------------------------------------------------------------|--------------------------|

| By:                   | Ataollah Mahsafar                                                                 |                          |

| Entitled:             | Design and Demonstration of Optical Logic Gates                                   | s with Electronic Inter- |

|                       | face for Optical Switching Applications                                           |                          |

| and submitted in p    | artial fulfillment of the requirements for the degree of                          |                          |

|                       | Master of Applied Science (Electrical Engineer                                    | ing)                     |

| complies with the     | regulations of this University and meets the accepted                             | standards with respect   |

| originality and qua   | ility.                                                                            |                          |

| Signed by the Fina    | d Examining Committee:                                                            |                          |

|                       |                                                                                   |                          |

|                       | Dr. John Xiupu Zhang                                                              | _ Chair                  |

|                       | Dr. Pablo Bianucci                                                                | External Examiner        |

|                       | Dr. John Xiupu Zhang                                                              | Examiner                 |

|                       | Dr. Glenn Cowan                                                                   | Supervisor               |

| Approved by           | Dr. Wahab Hamou-Lhadj, Chair<br>Department of Electrical and Computer Engineering |                          |

|                       | _ 2025                                                                            | Eng., Dean               |

Faculty of Engineering and Computer Science

to

#### **Abstract**

Design and Demonstration of Optical Logic Gates with Electronic Interface for Optical Switching Applications

#### Ataollah Mahsafar

The scalability of high-capacity networks increasingly depends on advances in switching technology. Optical switching, particularly using microring-based logic, offers a path to higher bandwidth and lower signal degradation while enabling compact, cascadable architectures.

This thesis presents a microring modulator (MRM)-based 2×2 optical switch built from cascadable optical logic gates (OLGs) with electronic control circuits. An OLG is a fundamental building block of optical computing systems, performing logic operations by manipulating optical signals rather than electrical ones, thereby leveraging the inherently higher speed and lower propagation loss of light. The OLG's functionality is validated through experimental measurements of power transfer characteristics (PTC), optical noise margins (ONMs), and fan-out performance. The 2×2 switch, implemented with seven interconnected OLGs, demonstrates the scalability of this approach for more complex optical logic networks.

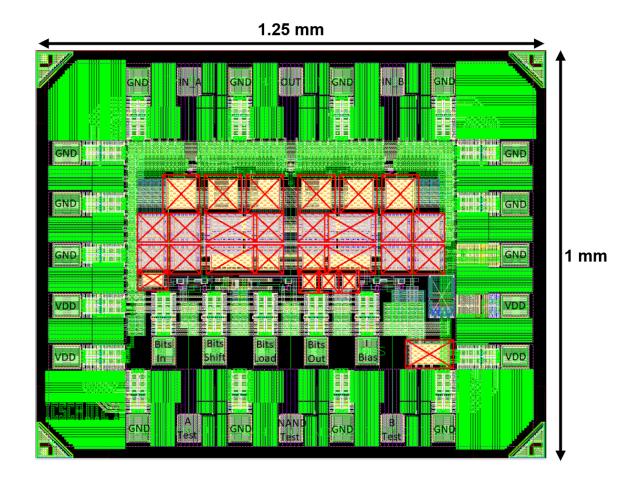

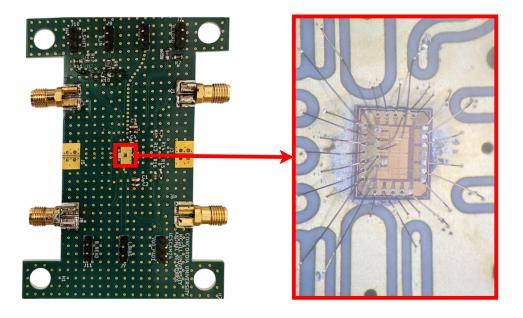

To enable higher-speed operation, a CMOS implementation of the electronic control circuit, for driving and processing optical-logic signals, was designed and fabricated in TSMC's 65 nm technology, occupying an active area of 1 mm × 1.25 mm. The design incorporates a peak/low detector-based offset compensation technique that ensures stable performance under unbalanced input data patterns. Post-layout simulations verify correct logic functionality, showing a simulated propagation delay of approximately 107 ps. Despite this delay, the standalone gate can process narrow pulses, corresponding to a data throughput of up to 8 Gbps.

The combined demonstration of discrete and integrated implementations highlights the potential

of microring-based optical switching as a scalable solution for future high-performance networking and computing systems.

## Acknowledgments

I would like to thank my supervisor, Prof. Glenn Cowan, for his guidance and expertise, which have been invaluable in completing this work. I am also grateful for the opportunity to be part of his energetic research group at Concordia University.

Furthermore, I sincerely appreciate the contributions of my collaborators, whose expertise and input have been instrumental in advancing this research. In particular, I acknowledge David Rolston, Prof. Odile Liboiron-Ladouceur, José García-Echeverría, and Daniel Musat for their notable contributions.

I am thankful to my friend and office-mate, Sara Radfar, for her thoughtful advice and will-ingness to help whenever needed throughout this journey. I also extend my thanks to the other members of our research group, particularly Abdullah Ibn Abbas, Di Zhang, and Vinicius Sirtoli, for their valuable knowledge sharing and support along the way.

I gratefully acknowledge the Canadian Microelectronics Corporation (CMC) for their assistance and support.

Finally, I am profoundly grateful to my parents for their endless love, sacrifices, and belief in me. Even though I have been far from them during these years, their constant encouragement and guidance have been the foundation of everything I have accomplished. I also extend my heartfelt thanks to my brother, Ali, whose support, understanding, and inspiration have been a source of strength throughout my academic journey. This accomplishment would not have been possible without their unwavering presence in my life, despite the distance.

## **Contents**

| Li | st of l          | Figures  |                                                                      | ix |  |  |

|----|------------------|----------|----------------------------------------------------------------------|----|--|--|

| Li | List of Tables x |          |                                                                      |    |  |  |

| 1  | Intr             | oductio  | o <b>n</b>                                                           | 1  |  |  |

|    | 1.1              | Motiva   | ation                                                                | 1  |  |  |

|    | 1.2              | Contri   | butions and publications                                             | 3  |  |  |

|    | 1.3              | Thesis   | s organization                                                       | 4  |  |  |

| 2  | Lite             | rature l | Review                                                               | 6  |  |  |

|    | 2.1              | Micro    | ring Resonators/ Modulators                                          | 6  |  |  |

|    | 2.2              | MRM      | Device Used in This Work                                             | 13 |  |  |

|    | 2.3              | Relate   | d Work on Optical Logic Gates                                        | 16 |  |  |

|    |                  | 2.3.1    | Optical Logic Gate Realization Using Zero-Bias Photonic Structures   | 16 |  |  |

|    |                  | 2.3.2    | Optical Logic Gate Realization Using Feedback-Controlled PN-Junction |    |  |  |

|    |                  |          | Tuning                                                               | 19 |  |  |

|    |                  | 2.3.3    | Non-MRM-Based Structures                                             | 22 |  |  |

|    | 2.4              | Logic    | control circuit components                                           | 24 |  |  |

|    |                  | 2.4.1    | I-V Conversion Circuits                                              | 25 |  |  |

|    |                  | 2.4.2    | Main Amplifiers (MAs)                                                | 31 |  |  |

|    |                  | 2.4.3    | DC Offset Compensation (DCOC)                                        | 34 |  |  |

|    | 2.5              | Concl    | usion                                                                | 37 |  |  |

| 3 | Desi | gn and  | Realization of a 2×2 Optical Switch Using Cascadable Optical Logic Gates  | 38  |

|---|------|---------|---------------------------------------------------------------------------|-----|

|   | 3.1  | Optica  | l Logic Gate Design and Characterization                                  | 38  |

|   |      | 3.1.1   | Cascadable Optical NOT Gate Design                                        | 39  |

|   |      | 3.1.2   | Cascadable Optical NAND Gate Design                                       | 44  |

|   |      | 3.1.3   | Logic Control Design                                                      | 45  |

|   |      | 3.1.4   | Power Transfer Characteristic, Optical Noise Margin, and Fan-out Measure- |     |

|   |      |         | ments                                                                     | 46  |

|   | 3.2  | 2×2 O   | ptical Switch Design and Characterization                                 | 52  |

|   |      | 3.2.1   | 2×2 Switch based on Optical Combinational Logic                           | 52  |

|   |      | 3.2.2   | 2×2 Optical Switch Measurements                                           | 53  |

|   | 3.3  | Conclu  | asion                                                                     | 58  |

| 4 | Desi | gn and  | Tapeout of the Proposed IC-Level Peak/Low Detector-Based Logic Control    |     |

|   | Circ | cuit    |                                                                           | 60  |

|   | 4.1  | Design  | of the Proposed Peak/Low Detector-Based Logic Control Circuit             | 64  |

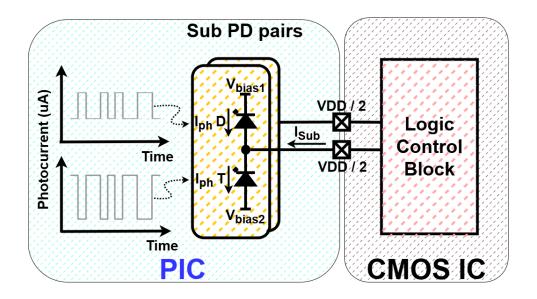

|   |      | 4.1.1   | Subtractive PD Pair Structure                                             | 66  |

|   |      | 4.1.2   | TIA Design                                                                | 67  |

|   |      | 4.1.3   | MA Design                                                                 | 70  |

|   |      | 4.1.4   | Proposaed DC Offset Compensation (DCOC) Design                            | 72  |

|   |      | 4.1.5   | NAND Gate and Output Inverter Design                                      | 85  |

|   | 4.2  | Post-L  | ayout Simulation Results                                                  | 87  |

|   |      | 4.2.1   | Behavior Under Input Densities of logical '1's from 10% to 90% in 10%     |     |

|   |      |         | Increments                                                                | 89  |

|   |      | 4.2.2   | Behavior Under a Direct Transition from 10% to 90% Input Density (Worst-  |     |

|   |      |         | Case Scenario)                                                            | 92  |

|   |      | 4.2.3   | High-Speed Functionality Test with Balanced Input Signals at 8 Gbps       | 96  |

|   |      | 4.2.4   | PTC and ONM Simulations for an Optical NOT                                | 99  |

|   | 4.3  | Floor l | Planning                                                                  | 100 |

|   | 44   | Measu   | rement Setup and Fabricated Chip Integration                              | 102 |

|    | 4.5    | Conclusion                                 | 103 |

|----|--------|--------------------------------------------|-----|

| 5  | Con    | clusions and Future Work                   | 105 |

|    | 5.1    | Comparision                                | 106 |

|    | 5.2    | Future Work                                | 109 |

| Aj | ppend  | ix A KiCad Design of the Logic Control PCB | 111 |

| Aj | ppend  | ix B KiCad Design of the High-Speed PCB    | 116 |

| Bi | bliogr | raphy                                      | 118 |

## **List of Figures**

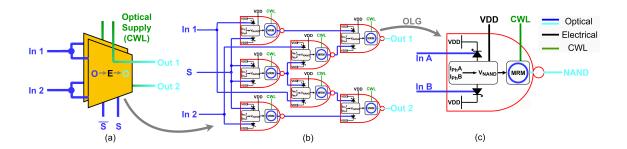

| Figure 1.1             | (a) Conceptual schematic of a cascadable 2×2 optical multiplexer (switch).                                     |    |

|------------------------|----------------------------------------------------------------------------------------------------------------|----|

| (b) Im                 | plementation using seven optical NAND gates with local regeneration. (c)                                       |    |

| Conce                  | ptual schematic of an optical NAND gate                                                                        | 3  |

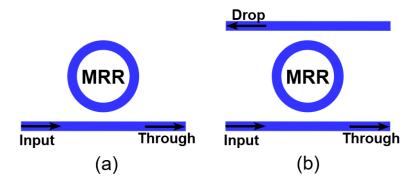

| Figure 2.1             | (a) Single-bus and (b) double-bus MRR configurations for optical signal                                        |    |

| routing                | Ţ                                                                                                              | 7  |

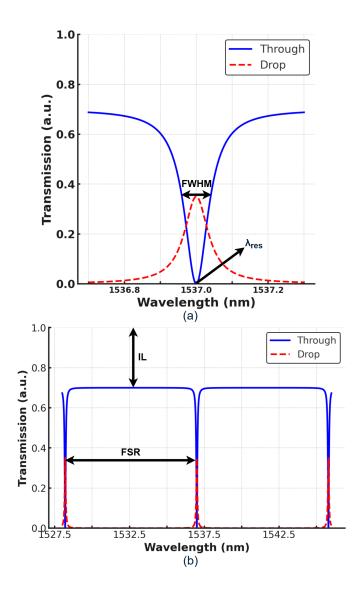

| Figure 2.2             | (a) Transmission spectrum of an MRR, illustrating resonance wavelength                                         |    |

| $(\lambda_{ m res})$ a | and full width at half maximum (FWHM), and (b) Periodic resonance occur-                                       |    |

| ring at                | free spectral range (FSR) intervals. The figure also indicates the insertion                                   |    |

| loss (II               | L)                                                                                                             | 9  |

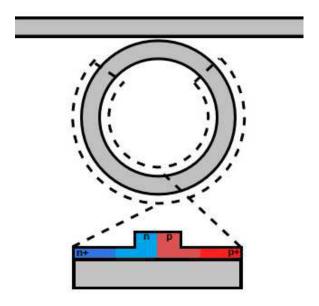

| Figure 2.3             | Structure of an MRM with an embedded pn-junction for electro-optic tuning                                      |    |

| [22]                   |                                                                                                                | 10 |

| Figure 2.4             | Differential transmission spectra of an MRM under varying reverse-bias volt-                                   |    |

| ages, s                | howing the resonance shift between the unbiased and reverse-biased states                                      | 11 |

| Figure 2.5             | Block diagram of the thermal control unit for MRM [24]                                                         | 12 |

| Figure 2.6             | (a) Micrograph of the fabricated MRM, and (b) measured transmission spec-                                      |    |

| tra at V               | $V_{\rm rb}$ = 0 V and $V_{\rm rb}$ = 5 V, highlighting the operating wavelength $\lambda_{\rm c}$ for differ- |    |

| ential l               | ogic operation                                                                                                 | 14 |

| Figure 2.7             | (a) Differential optical transmission $(T_T-T_D)$ measured for $V_{\rm rb}$ from 0 V                           |    |

| to 5 V,                | showing resonance shift, (b) linear relationship between $V_{ m rb}$ and differential                          |    |

| optical                | transmission $(T_T - T_D)$ , (c) electro-optic tuning of the resonance wavelength                              |    |

| versus                 | $V_{ m ph}$                                                                                                    | 15 |

| Figure 2.8 Zero-bias PD stack in the optical-to-voltage converter (OVC) used to drive            |    |

|--------------------------------------------------------------------------------------------------|----|

| an MRM without external electrical power [27]                                                    | 17 |

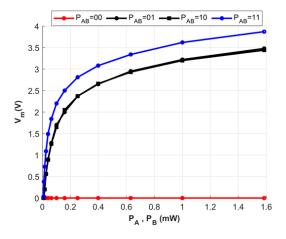

| Figure 2.9 Optical power-to-voltage characterization. Measured OVC output voltage as             |    |

| a function of input optical power ( $P_A$ or $P_B$ ) for different input logic $P_{AB}$ configu- |    |

| rations: 00, 01, 10, 11                                                                          | 18 |

| Figure 2.10 Operational principle of the zero-bias optical logic gate [27]. (a) OR gate          |    |

| implementation and (b) NOR gate implementation                                                   | 18 |

| Figure 2.11 PN-junction feedback-based control scheme for implementing optical logic             |    |

| gates using MRMs [20]. (a) Circuit schematic for NOR gate. (b) Operational prin-                 |    |

| ciple of NOR gate.                                                                               | 20 |

| Figure 2.12 QDSOA–MZI based all-optical NOR gate with corresponding truth table [11].            | 22 |

| Figure 2.13 Schematic of the Kerr-effect-based photonic crystal AND gate structure [29].         | 23 |

| Figure 2.14 Overall block diagram of the logic control circuit, illustrating its key func-       |    |

| tional components                                                                                | 25 |

| Figure 2.15 Resistor-based I–V conversion: (a) circuit schematic and (b) AC small-signal         |    |

| model                                                                                            | 26 |

| Figure 2.16 Minimal OLG using PD, resistor $R_C$ , and MRM                                       | 27 |

| Figure 2.17 CMOS inverter-based TIA: (a) circuit schematic and (b) small-signal model.           | 30 |

| Figure 2.18 Cherry–Hooper amplifier used as a main amplifier stage: (a) circuit schematic        |    |

| and (b) small-signal model                                                                       | 33 |

| Figure 2.19 Inverter-based DCOC circuit with low-pass filtering and feedback loop. (a)           |    |

| Circuit schematic with compensation current $I_{\rm OC}$ used to stabilize the baseline. (b)     |    |

| Output voltage $V_O$ without DCOC, showing baseline drift. (c) Output voltage $V_O$              |    |

| with DCOC, showing corrected baseline around $V_{\mathrm{DD}}/2$                                 | 35 |

| Figure 2.20 Pseudo-random signal between 300 mV and 700 mV with 50% logical '1'.                 |    |

| The black dashed line shows the midpoint (0.50 V) and the red dashed line the                    |    |

| average (0.503 V)                                                                                | 36 |

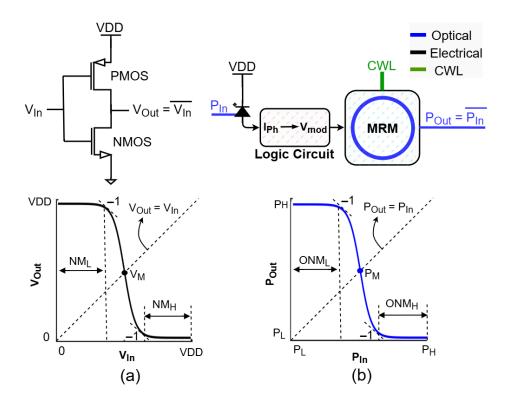

| Figure | 3.1      | (a) Schematic of a conventional digital NOT gate, showing the VTC and                 |    |

|--------|----------|---------------------------------------------------------------------------------------|----|

| n      | oise n   | nargins; (b) conceptual schematic of an optical NOT gate, illustrating the            |    |

| P      | PTC an   | nd its associated ONMs                                                                | 39 |

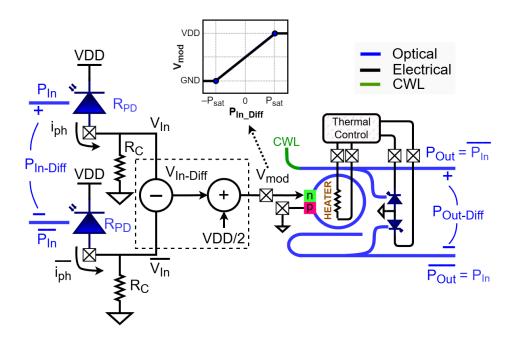

| Figure | 3.2      | conceptual schematic of a simplified logic control circuit for a differential         |    |

| o      | ptical   | inverter                                                                              | 42 |

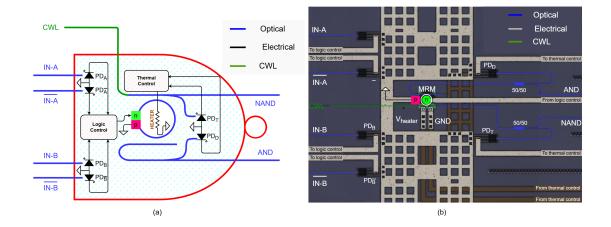

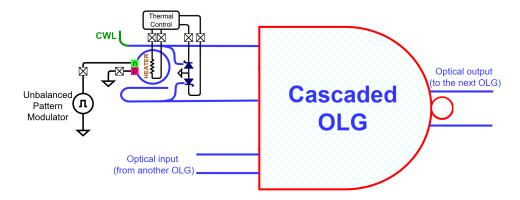

| Figure | 3.3      | (a) Schematic of the designed cascadable optical NAND gate, and (b) mi-               |    |

| c      | rograp   | oh of the fabricated PIC featuring a double-bus MRM, integrated PDs that              |    |

| re     | eceive   | optical input signals for logic control circuit, and monitoring PDs used for          |    |

| iı     | mplem    | nenting the thermal control circuit.                                                  | 45 |

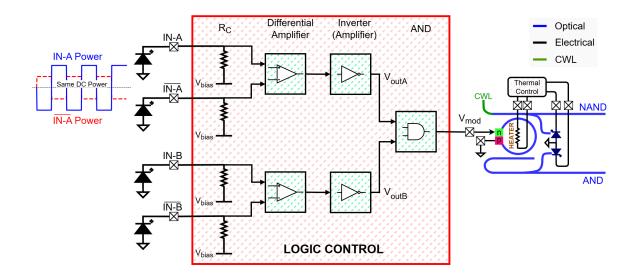

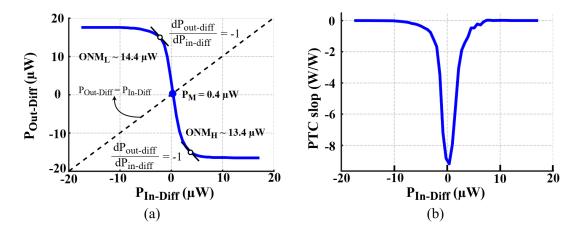

| Figure | 3.4      | Schematic of the electronic circuit designed to control each optical NAND             |    |

| g      | gate     |                                                                                       | 46 |

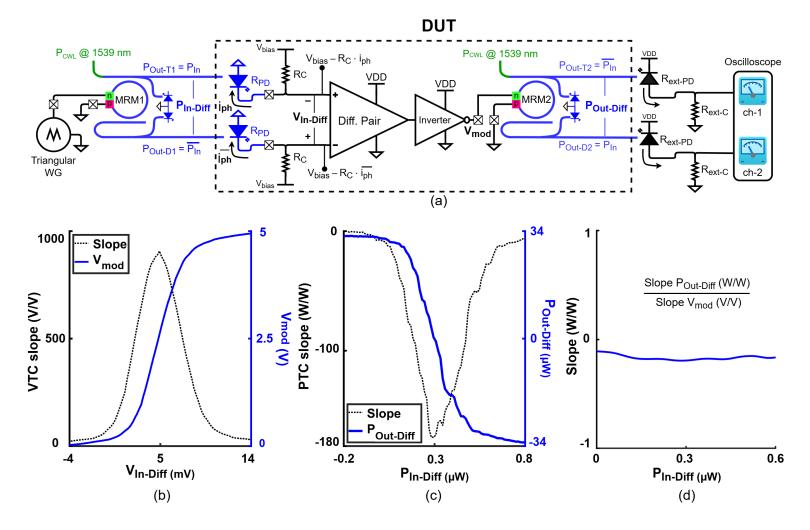

| Figure | 3.5      | (a) Experimental setup for measuring the PTC of the optical NOT gate, (b)             |    |

| n      | neasur   | ed VTC of the active electrical circuit and its slope, (c) measured PTC of the        |    |

| o      | ptical   | NOT gate and its slope, (d) system optical gain after removing the effect of          |    |

| tl     | he acti  | ve electrical circuit                                                                 | 49 |

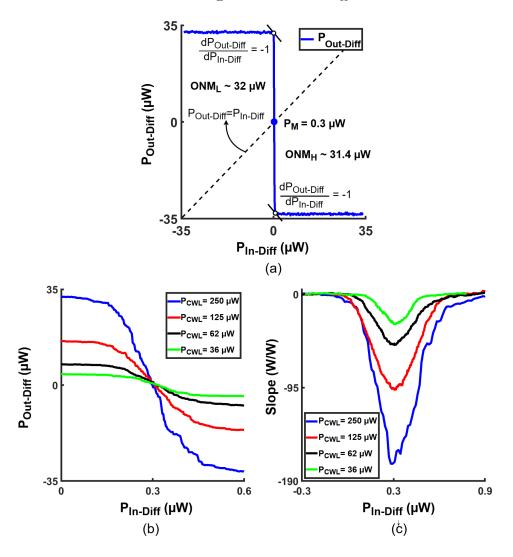

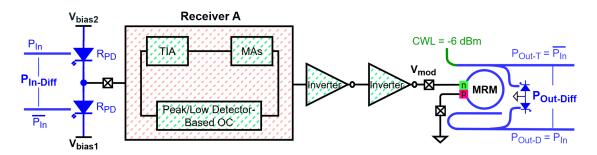

| Figure | 3.6      | (a) optical inverter PTC at a CW input power of $-6  \mathrm{dBm}$ , showing the full |    |

| iı     | nput ra  | ange and extracted ONMs. (b) PTC of the optical inverter under different              |    |

| C      | CW inp   | out powers, illustrating the decrease in output amplitude with reduced input          |    |

| p      | ower.    | And (c) corresponding slope variations of the inverter response as a function         |    |

| o      | of input | t power, highlighting the reduction in gain at lower powers                           | 50 |

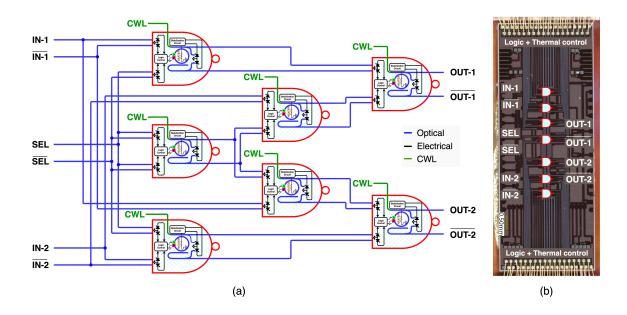

| Figure | 3.7      | (a) Schematic of the designed combinational logic to perform a 2×2 optical            |    |

| S      | witch    | function, and (b) micrograph of the manufactured photonic integrated circuit.         | 53 |

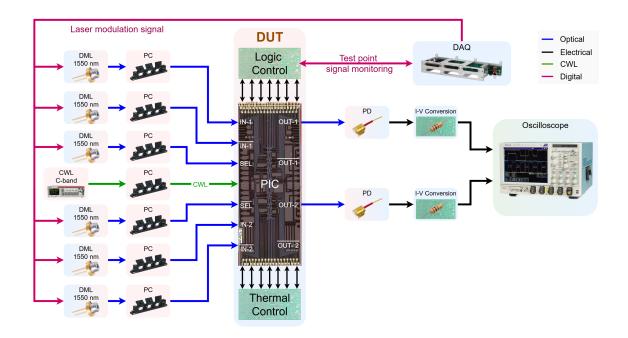

| Figure | 3.8      | Experimental setup to perform the MRM, logic control and 2×2 switch mea-              |    |

| S      | ureme    | nts including a CW C-band laser, DMLs, PCs, DAQ TS 15130 to generate                  |    |

| tl     | he opti  | ical input logic signals and monitor the logic control, the device under test         |    |

| (]     | DUT)     | consisting of the PIC and PCB logic control, QPhotonics QPFD-200 PDs,                 |    |

| 10     | ow-spe   | eed I-V conversion resistance in PCB, and an oscilloscope                             | 54 |

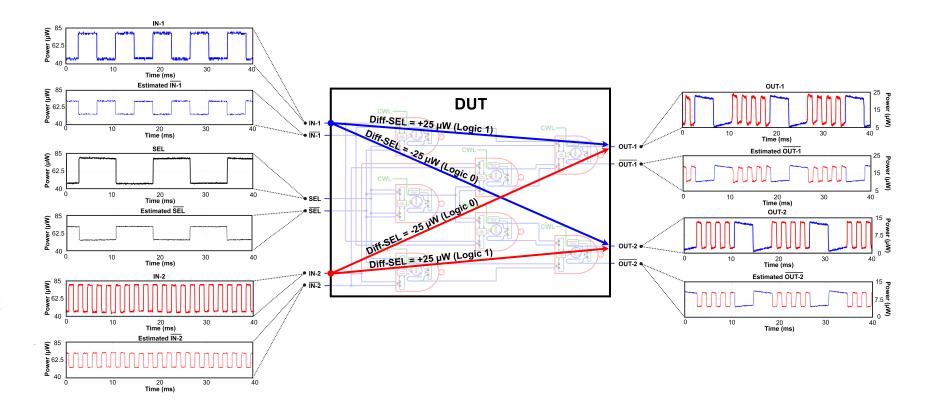

| Figure 3.9  | Measured through powers of IN-1, IN-2, SEL, OUT-1, and OUT-2, along                       |    |

|-------------|-------------------------------------------------------------------------------------------|----|

| with t      | heir estimated drop (complementary) powers, demonstrating the bar and cross               |    |

| functi      | onality of the 2×2 optical switch                                                         | 56 |

| Figure 4.1  | Schematic illustration of thermal locking behavior under unbalanced modu-                 |    |

| lation      |                                                                                           | 61 |

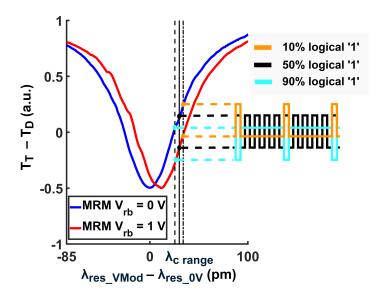

| Figure 4.2  | Measured differential transmission $(T_T - T_D)$ as a function of reverse bias            |    |

| voltag      | ge $V_{\rm rb}$ at 0 V and 1 V. The operating points corresponding to 10%, 50%, and       |    |

| 90% 1       | ogical '1' data densities are highlighted                                                 | 61 |

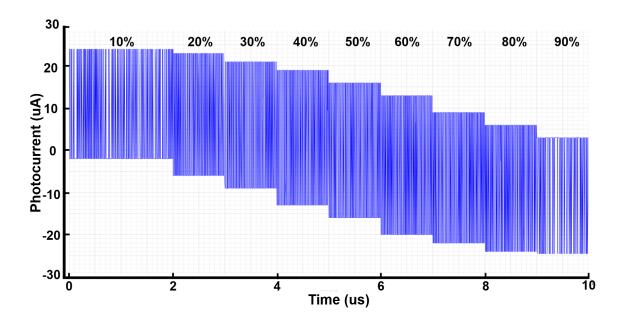

| Figure 4.3  | Simulated photocurrent at the input of the logic control circuit of the cas-              |    |

| caded       | OLG for densities of logical '1's ranging from 10% to 90%                                 | 63 |

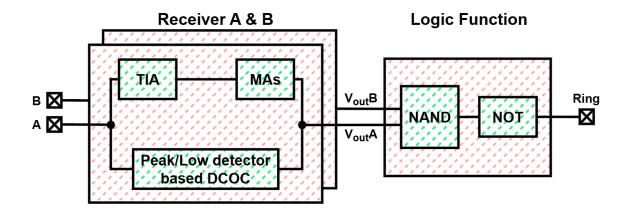

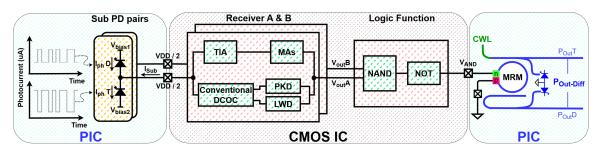

| Figure 4.4  | Block diagram of the proposed IC-level logic control circuit                              | 64 |

| Figure 4.5  | Subtractive PD Pair structure                                                             | 67 |

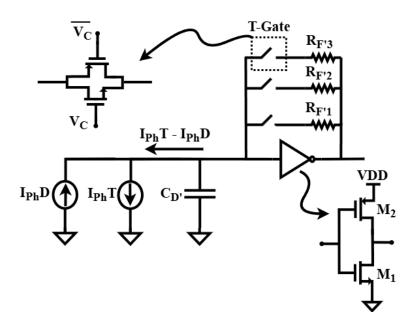

| Figure 4.6  | Schematic of the inverter-based TIA with selectable feedback resistors using              |    |

| a T-ga      | ate switching network                                                                     | 68 |

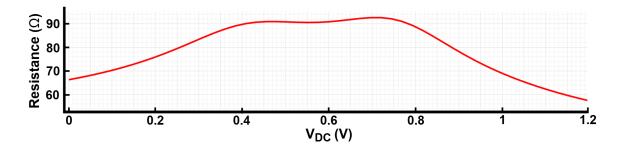

| Figure 4.7  | Simulated small-signal on-resistance of the T-gate switch with optimized                  |    |

| transis     | stor sizing, showing a relatively constant resistance over the $0 - 1.2 \text{ V}$ signal |    |

| range.      | The x-axis represents the DC voltage applied to both terminals of the switch.             | 69 |

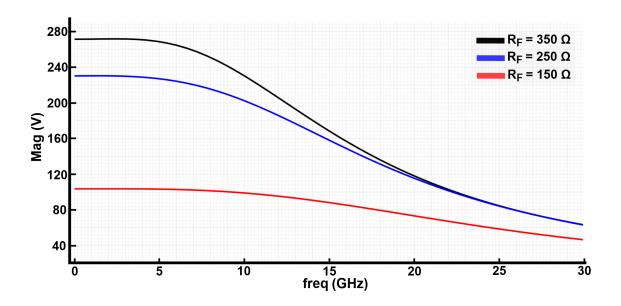

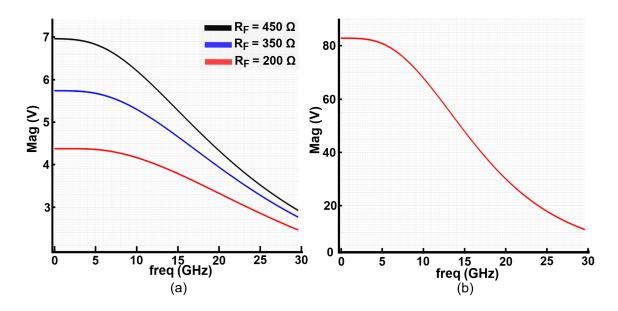

| Figure 4.8  | simulated AC response of the reconfigurable TIA for three different feedback              |    |

| resista     | ance settings.                                                                            | 70 |

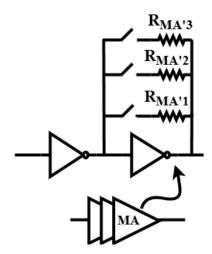

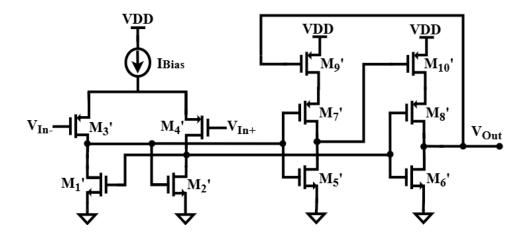

| Figure 4.9  | Schematic of the three-stage Cherry-Hooper main amplifier                                 | 71 |

| Figure 4.10 | (a) Simulated AC response of the MA for different feedback resistance set-                |    |

| tings.      | (b) Combined response of the full three-stage MA with $R_{\rm MA}=200~\Omega$ in all      |    |

| stages      |                                                                                           | 72 |

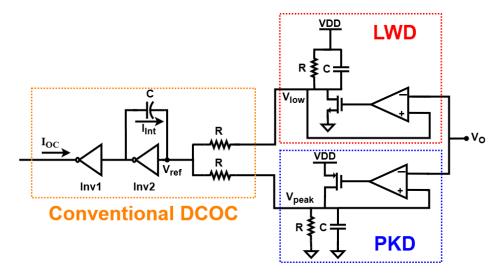

| Figure 4.11 | Block diagram of the proposed logic control circuit with accurate peak/low                |    |

| detect      | or-based DCOC                                                                             | 73 |

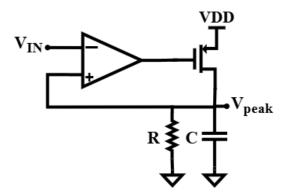

| Figure 4.12 | High-level schematic of the PKD circuit                                                   | 75 |

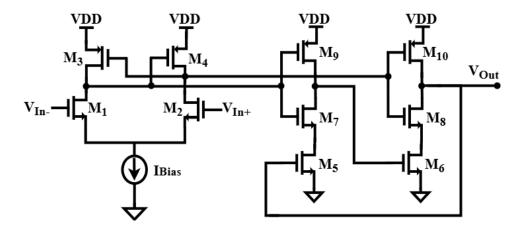

| Figure 4.13 | Schematic of the two-stage comparator used in the peak detector                           | 77 |

| Figure 4.14 | DC sweep of the stand-alone comparator, showing a sharp switch near 700                   |    |

| mV          |                                                                                           | 79 |

| Figure 4.15 Transient response to: (a) a 2 mV input step, (b) a 30 mV input step, (c) a        |    |

|------------------------------------------------------------------------------------------------|----|

| 400 mV input step. (d) Overdrive recovery test                                                 | 80 |

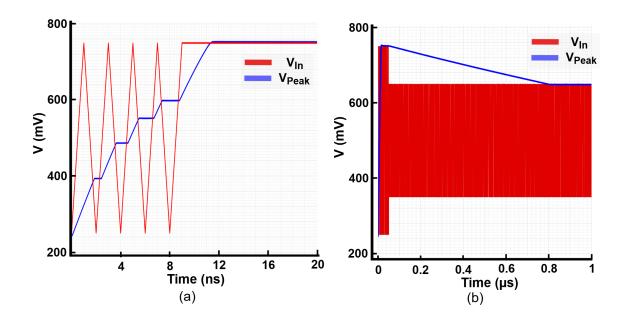

| Figure 4.16 Full PKD simulation with a triangular wave input: (a) tracking and hold            |    |

| operation; (b) decay and detection of a new peak                                               | 82 |

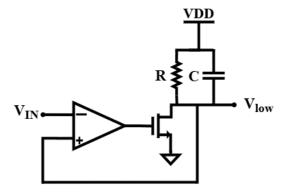

| Figure 4.17 High-level schematic of the LWD, complementary to the PKD                          | 83 |

| Figure 4.18 Schematic of the comparator used in the LWD circuit. It follows the same           |    |

| structure as the PKD comparator but with complementary devices                                 | 84 |

| Figure 4.19 Proposed DCOC block                                                                | 85 |

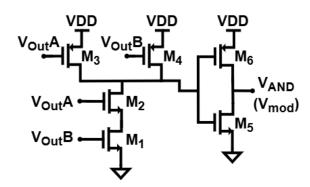

| Figure 4.20 Schematic of the electrical NAND gate followed by an inverter                      | 86 |

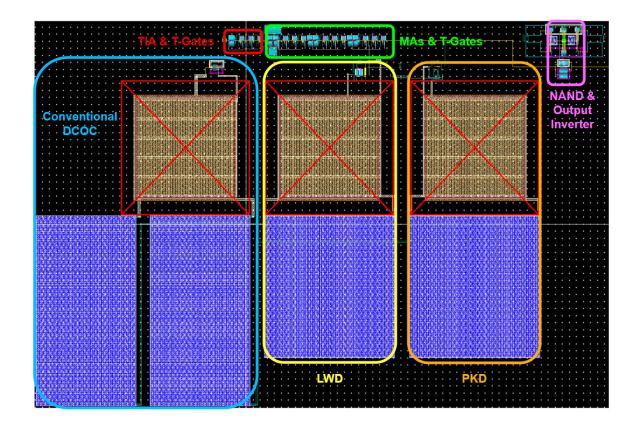

| Figure 4.21 Layout of one receiver arm of the proposed circuit (e.g., Arm A), along with       |    |

| the NAND gate and the output inverter                                                          | 88 |

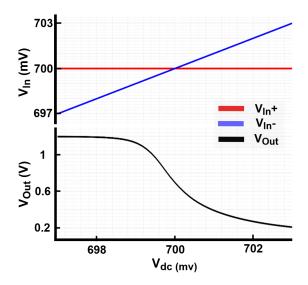

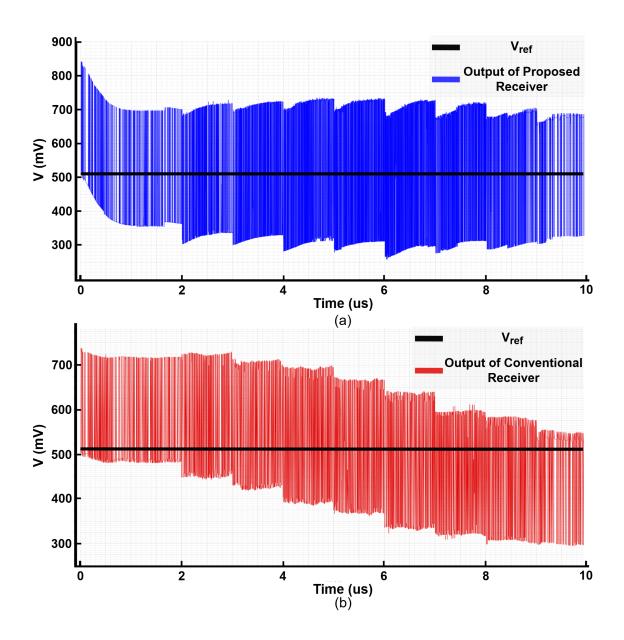

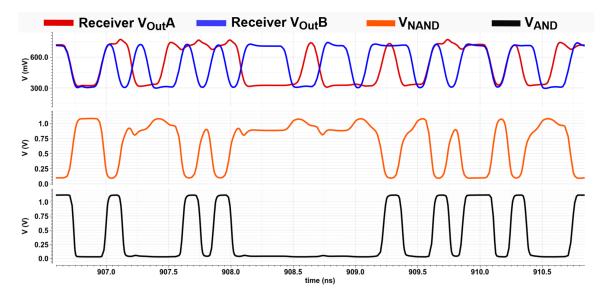

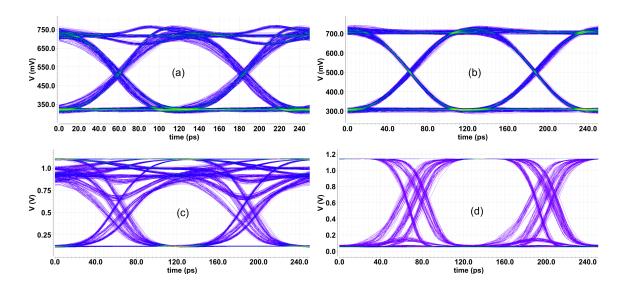

| Figure 4.22 Receiver output voltages under varying input data densities (10%–90%): (a)         |    |

| proposed receiver, (b) conventional receiver                                                   | 90 |

| Figure 4.23 Eye diagrams for the (a) proposed and (b) conventional receivers under vary-       |    |

| ing data densities                                                                             | 91 |

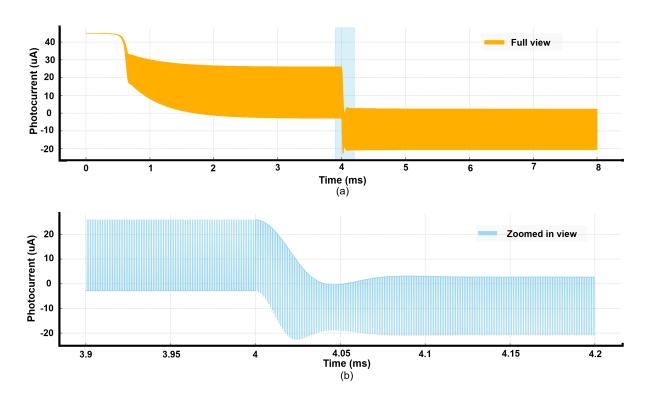

| Figure 4.24 Input photocurrent waveform showing a direct transition from 10% to 90%            |    |

| input density; (a) full view, (b) zoomed-in view                                               | 92 |

| Figure 4.25 Input bidirectional photocurrent with $10\times$ faster transition: from $10\%$ to |    |

| 90% logic '1' density (red curve) and from 90% to 10% logic '1' density (blue curve).          | 93 |

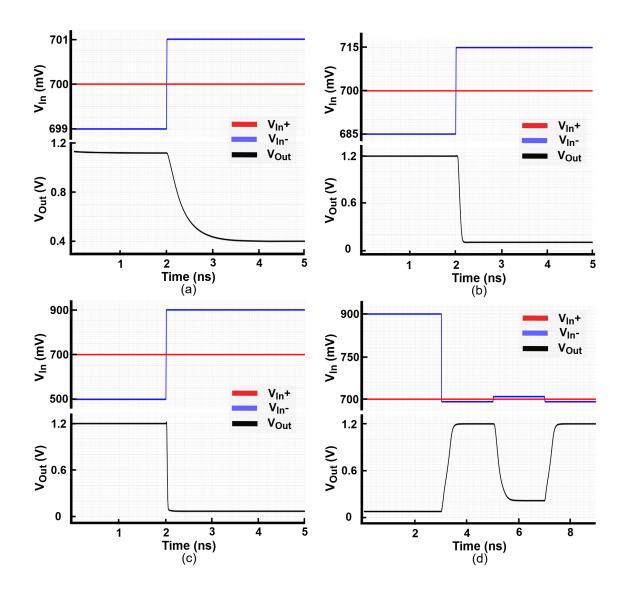

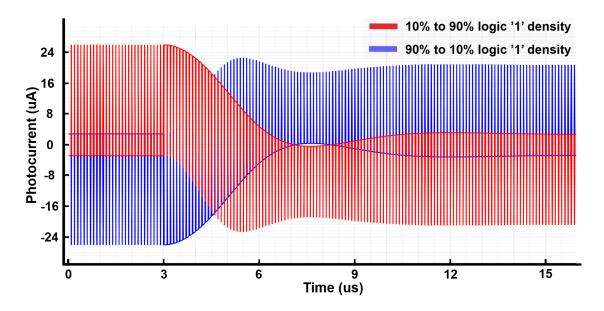

| Figure 4.26 (a) The proposed and (b) conventional receiver output during worst-case            |    |

| density (10% to 90% and 90% to 10%) transitions                                                | 95 |

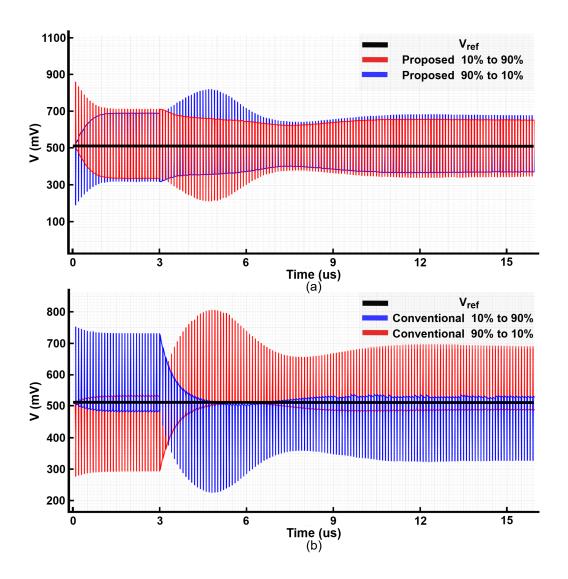

| Figure 4.27 Transient simulation results under 8 Gbps balanced input conditions showing        |    |

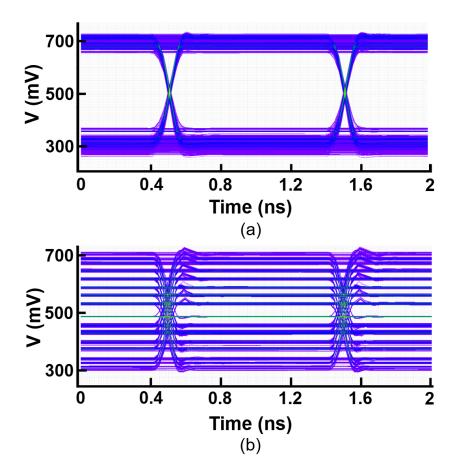

| the outputs of the two receiver arms, the NAND gate output, and the final AND signal.          | 97 |

| Figure 4.28 Eye diagrams under 8 Gbps balanced input signals (50% logical '1's): (a)           |    |

| Receiver Arm A output, (b) Receiver Arm B output, (c) NAND gate output, (d)                    |    |

| Final AND signal                                                                               | 98 |

| Figure 4.29 Schematic diagram of the simulated optical NOT gate configuration used for         |    |

| PTC and ONM analysis                                                                           | 90 |

| Figure 4.30 | Simulated results for the IC-level optical NOT gate: (a) PTC and (b) corre-   |     |

|-------------|-------------------------------------------------------------------------------|-----|

| spondi      | ing slope                                                                     | 100 |

| Figure 4.31 | Top-level block diagram view of the floor plan                                | 101 |

| Figure 4.32 | Layout of the complete logic control block, including pad ring and seal ring. | 102 |

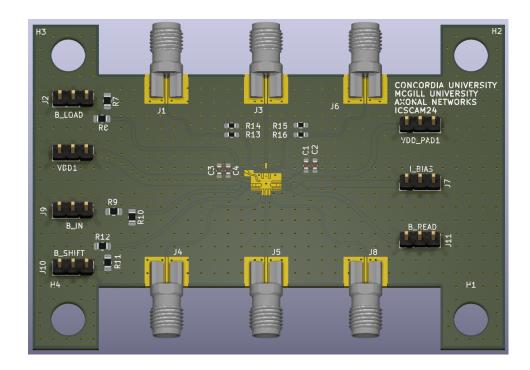

| Figure 4.33 | High-speed test PCB with the wire-bonded fabricated chip mounted for elec-    |     |

| trical r    | measurements                                                                  | 103 |

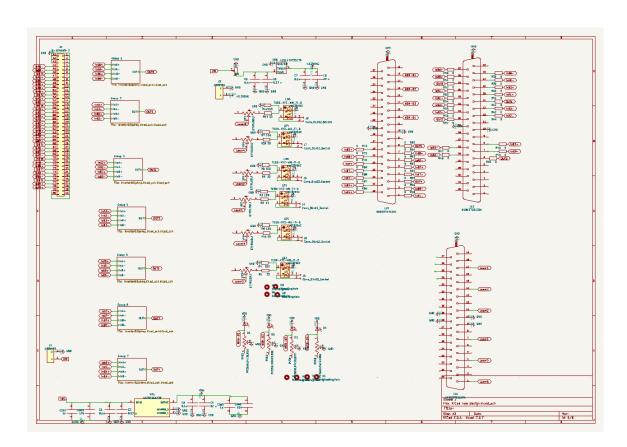

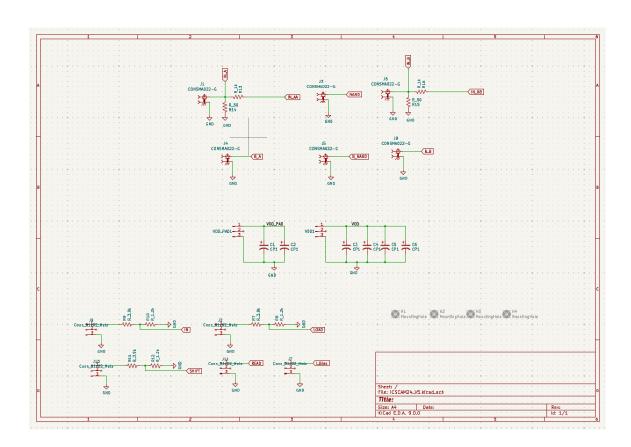

| Figure A.1  | High-level schematic of the logic control board used for the experiments in   |     |

| Chapte      | er III                                                                        | 111 |

| Figure A.2  | Detailed schematic of a single logic control board implementing one AND       |     |

| gate.       |                                                                               | 112 |

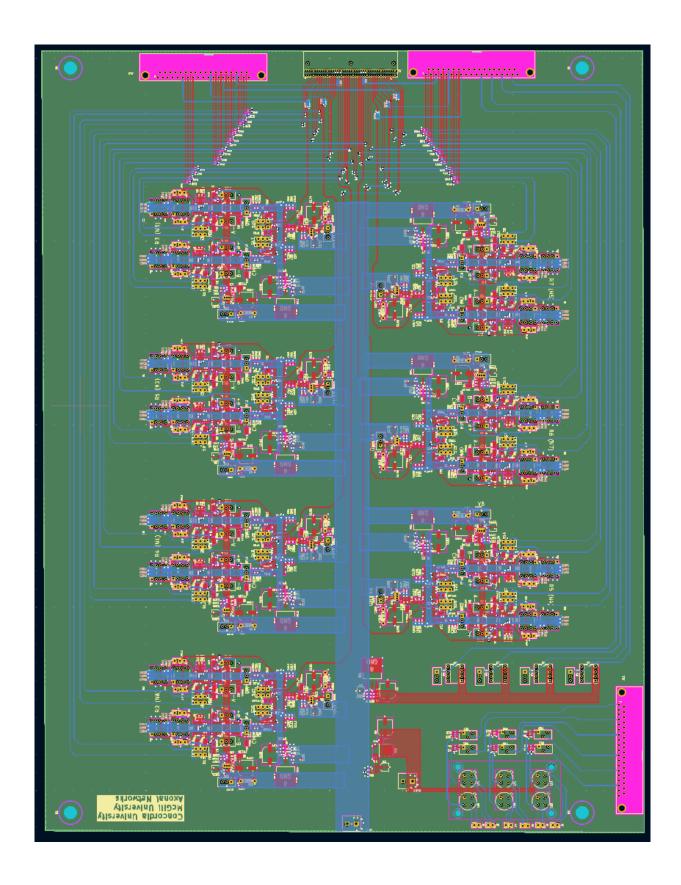

| Figure A.3  | PCB layout of the logic control board                                         | 113 |

| Figure A.4  | Fabricated logic control PCB                                                  | 114 |

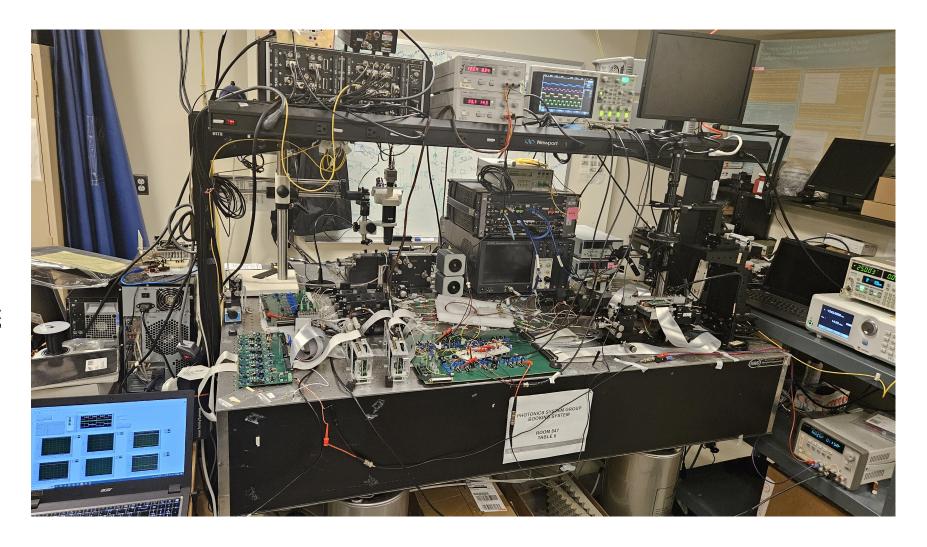

| Figure A.5  | Experimental setup of 2×2 optical switch                                      | 115 |

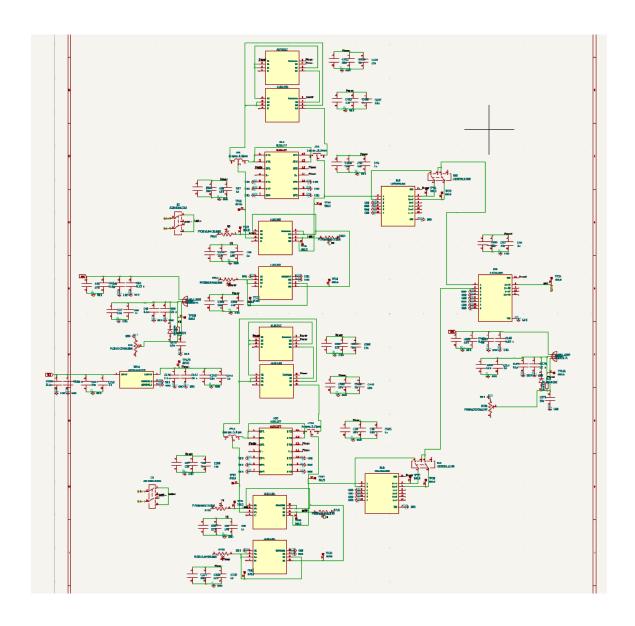

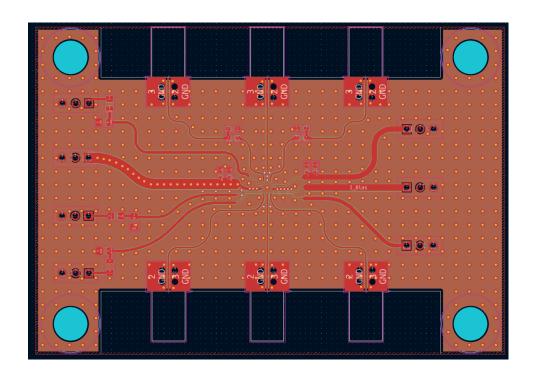

| Figure B.1  | High-speed PCB schematic                                                      | 116 |

| Figure B.2  | High-speed PCB design                                                         | 117 |

| Figure B.3  | 3D rendering of the high-speed PCB design                                     | 117 |

## **List of Tables**

| Table 3.1 | Truth table of the $2\times2$ optical switch      | • | • | • |  | • | • | <br>• |  | 53  |

|-----------|---------------------------------------------------|---|---|---|--|---|---|-------|--|-----|

| Table 5.1 | Comparison of optical logic gate implementations. |   |   |   |  |   |   |       |  | 108 |

## **Chapter 1**

### Introduction

#### 1.1 Motivation

The growing demand for faster and more scalable computing and communication systems has fueled the exploration of novel logic architectures beyond conventional electronics. In traditional CMOS technology, although transistor delays continue to shrink, interconnect delays have become a dominant performance bottleneck [1, 2]. As a result, research has increasingly turned toward complementary approaches such as optical logic gates (OLGs) and optical switches, which leverage the natural advantages of light, including high speed, parallelism, low loss interconnects, and low crosstalk, and can be integrated with electronics through CMOS-compatible platforms [3, 4, 5, 6, 7, 8]. By employing optical interconnects, different stages of a system can be physically distributed across a larger area, reducing local power density and thermal hotspots. Additionally, distributing the electronic circuitry in such hybrid systems mitigates global electromagnetic interference (EMI) issues that often arise in dense electronic circuits. This level of physical separation and signal integrity management is difficult to achieve with conventional electrical interconnects, which suffer from higher losses and tighter integration constraints.

To realize these advantages at the logic level, various platforms have been explored for optical gates, including nonlinear effects [9], interferometers [10], SOAs [11], and photonic crystals [8, 12]. Among these, silicon photonics has emerged as a leading platform due to its compatibility with standard CMOS processes [7, 13], enabling close integration with electronics. This hybrid approach

allows scalable, cost-effective systems that combine the strengths of both photonics and electronics [14].

Microring modulators (MRMs) are particularly attractive for building optical logic gates. They have a small footprint, low power dissipation, and can operate at very high speeds [15], [16], [17]. Recent advances have demonstrated MRMs achieving over 200 Gbps data rates [15], making them strong candidates for future optical computing and optical interconnects.

Although many optical logic gates have been demonstrated individually, cascading them into larger systems remains a significant challenge. Insertion loss (IL) accumulates across stages, and without local signal regeneration using a fresh optical supply, signal quality rapidly degrades. This issue also affects existing switching architectures, such as Mach-Zehnder interferometer (MZI) switches [18], which route the same optical signal through multiple stages without regeneration, limiting scalability. Overcoming this bottleneck requires architectures with local optical signal regeneration at each stage.

Fig. 1.1 illustrates the core concept of our approach, showing (a) a modular, cascadable 2×2 optical multiplexer (switch), (b) its implementation using seven optical NAND gates, and (c) a conceptual schematic of an optical NAND gate constructed with MRMs and electronic control circuits. Each gate incorporates local signal regeneration, ensuring that every stage produces a fresh optical signal. Thus, while the output logically depends on the input, its power and signal integrity are independent of the input optical power, effectively avoiding cumulative IL. Thanks to fully optical interconnections between stages, larger switching networks built from these gates can operate at the speed of a single gate without performance degradation.

Figure 1.1: (a) Conceptual schematic of a cascadable 2×2 optical multiplexer (switch). (b) Implementation using seven optical NAND gates with local regeneration. (c) Conceptual schematic of an optical NAND gate.

#### 1.2 Contributions and publications

In this work, we present the design, fabrication, and experimental demonstration of a multistage optical logic system based on cascadable MRMs, integrated with a dedicated electronic logic control circuit that processes photodetector (PD) outputs and generates drive voltages to modulate the MRMs according to the desired logic function, thereby enabling scalable optical operations. The system comprises seven interconnected gates forming a 2×2 optical switch, with regenerative behavior and logic-level performance. We experimentally verify key logic metrics for the optical system, including optical power transfer characteristics (PTC) and optical noise margins (ONM), establishing a direct analogy to conventional electronic logic gates. While previous works have explored high-speed [15], low-voltage [16], and wideband MRMs [17], and others have demonstrated or simulated optical logic gates using various platforms [19, 12, 20], they often lack cascaded architectures or logic-level analysis. A recent study demonstrates an MRM-based photonic latch [21], though the latch itself is not experimentally demonstrated. To our knowledge, this work presents the largest experimental demonstration of a cascaded MRM-based optical logic system to date.

The successful PCB implementation and testing validated the proposed approach for realizing optical logic gates using MRMs together with a logic control circuit. These results provide strong evidence supporting the feasibility of developing an integrated chip for the logic control block,

capable of operating at higher data rates and handling input data streams with unbalanced densities of 1s and 0s. As a result, a CMOS chip implementing the logic control circuit has been designed and taped out using TSMC's 65 nm CMOS technology.

A journal paper based on the research presented in this thesis is currently being finalized for submission as the primary publication arising from this work:

• A. Mahsafar, J. G. Echeverría, D. Musat, D. Rolston, O. Liboiron-Ladouceur, and G. Cowan, "2×2 Optical Switch Based on Combinational Logic with Microring Modulators," in preparation for submission to *Journal of Lightwave Technology*.

Additional publications (published and in preparation) and patents related to aspects of this research include:

- D. Musat, J. G. Echeverría, **A. Mahsafar**, D. Rolston, O. Liboiron-Ladouceur, and G. Cowan, "Calibration-free Stabilization Circuit for Silicon Photonics Microring Modulators," in preparation for submission to *IEEE Transactions on Circuits and Systems I: Regular Papers*.

- J. G. Echeverría, D. Musat, A. Mahsafar, K. R. Mojaver, D. Rolston, G. Cowan, and O. Liboiron-Ladouceur, "Self-Calibrated Microring Weight Function for Neuromorphic Optical Computing," *Journal of Lightwave Technology*, vol. 43, no. 2, pp. 602–610, Jan. 15, 2025, doi: 10.1109/JLT.2024.3462534.

- Provisional Patent Application, Serial No. 63/550,369, filed February 6, 2024.

- International PCT Application, Serial No. PCT/CA2025/050148, filed February 5, 2025.

#### 1.3 Thesis organization

Chapter 2 introduces the fundamentals of microring resonators (MRRs) and MRMs, outlines the MRM device and thermal control method employed in this work, and reviews prior optical logic gate implementations based on these devices. It concludes with an overview of the key logic control circuit components relevant to this study. Chapter 3 describes the design of cascadable optical NOT and NAND gates, the logic control circuitry, and the 2×2 optical switch. It also presents

experimental results of individual logic gates and the full switch. Chapter 4 details the design and tape-out of a CMOS chip featuring an offset compensation technique in the logic control block, enabling reliable operation under unbalanced input data conditions at high data rates. Chapter 5 concludes the thesis by summarizing the key contributions and suggesting future research directions.

## Chapter 2

### **Literature Review**

This chapter begins by introducing the foundational concepts required to understand the operation of MRRs and MRMs, followed by a description of the specific MRM device and thermal control method employed in this work. It then reviews previous works on optical logic gates implemented using these devices, with particular emphasis on the design and structure of their logic control circuits, which process PD outputs and generate drive voltages for the modulators, as well as the associated challenges. Finally, it discusses the key components of logic control circuits commonly used in optical platforms.

#### 2.1 Microring Resonators/ Modulators

As shown in Fig. 2.1 (a) and (b), MRRs are compact and ring-shaped waveguides that are typically implemented in either a single-bus or double-bus configuration, where light is coupled from a straight waveguide into the ring [22].

Figure 2.1: (a) Single-bus and (b) double-bus MRR configurations for optical signal routing.

In the single-bus configuration, the ring is coupled to only one straight waveguide. In the double-bus setup, an additional waveguide is placed on the opposite side of the ring, introducing a drop port alongside the through port. These configurations determine how light at different wavelengths interacts with the ring, controlling whether it continues through the bus waveguide or is coupled into the ring and redirected to the drop port.

To achieve resonance within the microring cavity, the round-trip optical path must satisfy a phase-matching condition: the total distance traveled by the light in one loop must equal an integer multiple of its wavelength. This condition is expressed as:

$$\lambda_{\text{res}} = \frac{n_{\text{eff}}L}{m} \tag{1}$$

where  $\lambda_{\text{res}}$  is the resonant wavelength,  $n_{\text{eff}}$  is the effective refractive index, L is the ring's optical path length (circumference), and m is a positive integer. This relationship indicates that multiple wavelengths can meet the resonance condition, each corresponding to a different resonance order defined by the integer m. The spacing between these resonances is referred to as the free spectral range (FSR), and it depends on the geometry and effective index of the ring.

Fig. 2.2 (a) shows a representative transmission spectrum of the through and drop ports in a double-bus MRR when a continuous-wave laser (CWL) is swept across the wavelength range. For the single-bus configuration, the through-port response remains similar, but no drop-port curve is present, as the drop port does not exist in that setup. As shown in this figure, in the single-bus

configuration, destructive interference occurs at resonance, resulting in a sharp notch in the transmission spectrum at the through port. Off-resonant wavelengths continue through the waveguide with minimal loss. This configuration is compact and well-suited for applications where only spectral selection is required. The double-bus configuration adds a second waveguide, forming a drop port. At resonance, a portion of the optical power goes from the input waveguide into the ring and then is transferred to the drop port. Light that does not satisfy the resonance condition remains in the through port [22].

Figure 2.2: (a) Transmission spectrum of an MRR, illustrating resonance wavelength ( $\lambda_{\rm res}$ ) and full width at half maximum (FWHM), and (b) Periodic resonance occurring at free spectral range (FSR) intervals. The figure also indicates the insertion loss (IL).

Fig. 2.2 (a) and (b) also highlight several key parameters that influence its performance in photonic circuits. As discussed earlier, the resonant wavelength ( $\lambda_{res}$ ) corresponds to the specific wavelength at which light interferes destructively at the through port. Another important metric is the full width at half maximum (FWHM), which defines the spectral width of the resonance notch at half its maximum depth. A smaller FWHM indicates a sharper and more selective resonance. In

addition to these parameters, the insertion loss (IL) represents the optical power lost due to absorption, scattering, or imperfect coupling in the microring structure, measured away from resonance. Also, the quality factor (Q) provides a measure of the sharpness of the resonance. A high Q factor corresponds to a narrow resonance bandwidth and is defined as follows:

$$Q = \frac{\lambda_{\text{res}}}{FWHM} \tag{2}$$

Fig. 2.3 shows the structure of a typical MRM based on a pn-junction embedded inside the ring. MRMs are derived from MRRs but are designed for active tuning of the resonance. This is typically achieved by modifying the refractive index of the ring waveguide via the carrier plasma dispersion effect under electrical bias [23].

Figure 2.3: Structure of an MRM with an embedded pn-junction for electro-optic tuning [22].

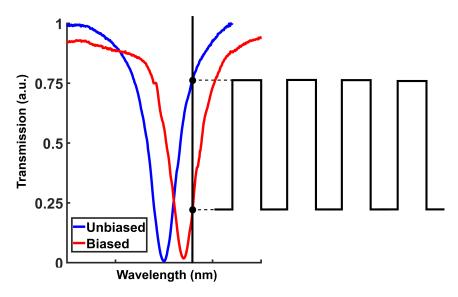

Fig. 2.4 shows the through-port transmission spectrum of an MRM measured under both unbiased and reverse-biased conditions, highlighting how the curve shifts with applied voltage. As the reverse bias increases, the resonance wavelength shifts along the wavelength axis. This behavior results from changes in the carrier concentration within the ring waveguide, which alter the refractive index. Since the resonant wavelength depends on the effective refractive index, applying a reverse-bias voltage shifts the resonance condition. As a result, a given input wavelength may move from

an off-resonant to a resonant state (or vice versa), enabling modulation of the optical signal [23]. In this way, the MRM operates as an optical modulator. The effectiveness of an MRM is characterized by several key parameters. The extinction ratio (ER) refers to the ratio of transmitted optical power between the logic '1' and logic '0' levels at the through port. A higher ER indicates better contrast between logic states and thus improved signal integrity. The modulation efficiency refers to the voltage required to achieve a desired shift in resonance wavelength. More efficient MRMs require less drive voltage.

Figure 2.4: Differential transmission spectra of an MRM under varying reverse-bias voltages, showing the resonance shift between the unbiased and reverse-biased states.

MRRs and MRMs are highly sensitive to both fabrication-induced variations and changes in ambient temperature, posing a major challenge for reliable operation. To maintain the desired resonance condition despite these variations, the modulator must be equipped with an effective tuning mechanism that ensures alignment with the target wavelength.

A commonly used approach is to exploit the thermo-optic properties of silicon [23]. By placing a microheater adjacent to the ring, the local temperature can be increased to shift the resonance [24]. It should be noted that this method allows only heating; there is no active cooling mechanism. As a result, continuous heating is required to maintain resonance alignment, which can contribute to increased energy usage over time [22].

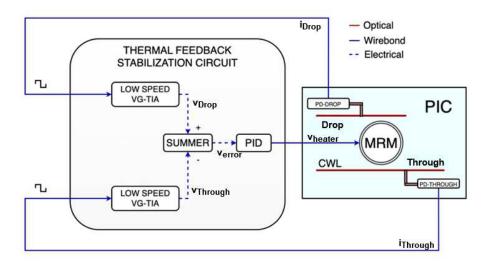

Fig. 2.5 shows the thermal feedback stabilization block diagram presented in [25]. In this approach, the optical powers at the through and drop ports of the MRM are monitored using low-speed, variable-gain transimpedance amplifiers (TIAs) connected to PDs integrated within the photonic integrated circuit (PIC). These electrical outputs ( $V_{\rm Through}$  and  $V_{\rm Drop}$ ) are subtracted in a summer block to generate an error signal ( $V_{\rm error}$ ) that reflects the balance between the two ports. When the microring operates at the optimal locking point, the average through and drop powers are equal, yielding  $V_{\rm error}=0$ .

This error signal is fed into an analog proportional-integral-derivative (PID) controller, which regulates the voltage applied to an integrated microheater ( $V_{\rm heater}$ ). By increasing or decreasing heater power, the resonance condition is thermally tuned through the thermo-optic effect, driving the error signal toward zero and locking the microring at the desired operating point. Since this scheme derives its reference internally from the device's own optical behavior, it eliminates the need for external calibration, making it inherently robust to temperature drift, fabrication variations, and laser power fluctuations.

Figure 2.5: Block diagram of the thermal control unit for MRM [24].

This thermal control circuit, designed by Daniel Musat, a Ph.D. student at Concordia University, is employed in this work to maintain stable MRM operation.

#### 2.2 MRM Device Used in This Work

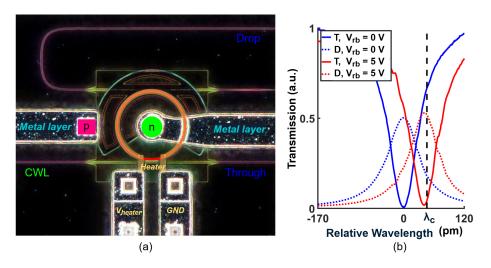

The MRM used in this work is based on the design reported in [26] and was fabricated by José García Echeverría, a Ph.D. candidate at McGill University, on a silicon-on-insulator (SOI) platform using a double-bus configuration, with a measured optical insertion loss of approximately 2dB. The author contributed to the collaborative optical and electro-optic characterization of the device, the results of which are presented in this section to provide context for the implementation described in Chapter 3.

Fig. 2.6 (a) shows the micrograph of the fabricated MRM. The metal interconnect layers extend to the bondpads of the PIC, which are wirebonded to the printed circuit board (PCB) and interfaced with the MRM driver through an off-board electrical connection. In this setup, the p-type side of the pn junction was grounded, and the n-type side was biased with a positive voltage. For static (DC) biasing, this voltage is denoted as  $V_{\rm rb}$ . Increasing  $V_{\rm rb}$  expands the depletion region and shifts the resonance wavelength.

The OLG structure that will be introduced in Chapter 3 operates with a 0–5 V single-ended electrical drive, while the logic functionality is realized through complementary optical powers at the through and drop ports. While the detailed rationale for this architecture and drive voltage will be presented in later sections, these assumptions are stated here to establish the context for the following MRM characterization.

The differential transmission is defined as the optical power difference between the through and drop ports of the microring, evaluated at a fixed wavelength. Near resonance, this difference can be well approximated by a Lorentzian function [27]:

$$T_{\text{Out-Diff}}(\lambda) = T_T(\lambda) - T_D(\lambda) = 1 - \frac{(T+D)}{1 + 4\left(\frac{\lambda - \lambda_{\text{res}}}{\text{FWHM}}\right)^2}$$

(3)

where T indicates the ring's intrinsic extinction (with T=1 for a critically coupled device), and D represents the coupling to the drop port. This Lorentzian approximation offers a compact and accurate description of the spectral response and will be referenced in the analysis of modulation behavior in Section 3.

While the Lorentzian model in (3) describes the differential transmission behavior, Fig. 2.6 (b)

shows the individual transmission spectra of the through and drop ports under two biasing conditions:  $V_{\rm rb}=0\,{\rm V}$  and  $V_{\rm rb}=5\,{\rm V}$ . As explained, the employed thermal control circuit locks the ring at a wavelength where the average powers at the through and drop ports are equal, corresponding to identical DC power levels. Since the drop port response is the inversion of the through port, this locking condition ensures that the through and drop outputs are approximately complementary. Consequently, the MRM must operate at a wavelength that satisfies

$$T_T(0V) - T_D(0V) = T_D(-5V) - T_T(-5V)$$

(4)

The operating wavelength satisfying (4) is indicated in Fig. 2.6 (b) as  $\lambda_c$ .

Figure 2.6: (a) Micrograph of the fabricated MRM, and (b) measured transmission spectra at  $V_{\rm rb}$  = 0 V and  $V_{\rm rb}$  = 5 V, highlighting the operating wavelength  $\lambda_{\rm c}$  for differential logic operation.

The MRM is first characterized by measuring its optical spectrum at 19 °C with no applied reverse bias ( $V_{\rm rb}=0~V$ ). From the through-port transmission spectrum at 0 V shown in Fig. 2.6 (b), a FWHM of 70 pm is measured, corresponding to a quality factor (Q) of 22,000. The extinction ratio (ER), measured from the same spectrum, is approximately 23 dB. The measured Q-factor translates into an optical bandwidth,  $f_{ph}$ , of approximately 8.75 GHz. As shown in Fig. 2.7 (a), the differential transmission ( $T_T-T_D$ ) is measured for  $V_{\rm rb}$  from 0 V to 5 V in 1 V steps. The plot illustrates the resonance shift with  $V_{\rm rb}$  and highlights the target operating wavelength, at which the differential

transmission is extracted for each bias level. These values are then used in Fig. 2.7 (b) to analyze the relationship between  $V_{\rm rb}$  and  $T_T-T_D$ , showing a slope of approximately – 0.2 a.u./V within the tested voltage range. Additionally, Fig. 2.7 (c) presents the electro-optic modulation behavior, where the resonance wavelength is tracked as a function of  $V_{\rm rb}$ . This characterization yields a tuning slope of approximately 8 pm/V. These results establish the device operating parameters used later in Chapter 3 and 4.

Figure 2.7: (a) Differential optical transmission  $(T_T - T_D)$  measured for  $V_{\rm rb}$  from 0 V to 5 V, showing resonance shift, (b) linear relationship between  $V_{\rm rb}$  and differential optical transmission  $(T_T - T_D)$ , (c) electro-optic tuning of the resonance wavelength versus  $V_{\rm rb}$ .

#### 2.3 Related Work on Optical Logic Gates

Optical logic gates have been implemented using diverse photonic device platforms, each exploiting distinct physical mechanisms. The primary focus of this section is on MRM-based approaches, which have been studied for their compactness and CMOS compatibility. In parallel, non-MRM structures, such as SOA–MZI and photonic crystal devices, have also been reported. Together, these works illustrate both the potential and the challenges of optical logic design. The following subsections review representative examples from both categories, highlighting their operating principles, architectural assumptions, and integration challenges.

#### 2.3.1 Optical Logic Gate Realization Using Zero-Bias Photonic Structures

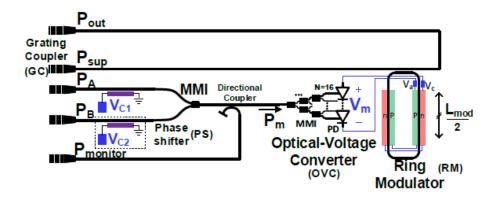

As illustrated in Fig. 2.8, [28] proposed a universal all-optical logic gate capable of operating without any electrical power supply. The architecture combines the optical inputs in a multimode interference (MMI) coupler, which forms the central stage of operation. Before reaching the MMI, the signals  $P_A$  and  $P_B$  pass through thermo-optic phase shifters controlled by voltages  $V_{C1}$  and  $V_{C2}$ . To realize OR and NOR functions, these phase shifters align the two inputs so that they arrive in phase, ensuring constructive addition inside the MMI. The resulting combined optical power  $P_m$  is then delivered to the optical-to-voltage converter (OVC).

The OVC, built from a stack of 16 series-connected zero-biased photodiodes, performs a non-linear optical-power-to-voltage conversion. The generated voltage  $(V_m)$  subsequently drives the MRM. If the ring's resonance aligns with the supply wavelength  $P_{\text{sup}}$ , the light is dropped and does not reach the output waveguide, corresponding to a logical "0." Otherwise, the light passes through to the output, representing a logical "1." By adjusting the initial resonance condition, the structure can be configured to implement OR or NOR logic, depending on the chosen biasing scheme.

Figure 2.8: Zero-bias PD stack in the optical-to-voltage converter (OVC) used to drive an MRM without external electrical power [27].

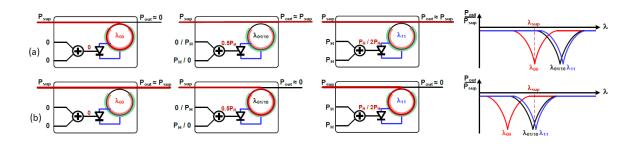

To realize logic operations such as OR and NOR, the system exploits the nonlinear relationship between the combined input power  $P_m$  and the modulation voltage  $V_m$ , which in turn shifts the resonance of the MRM. Fig. 2.9 shows this nonlinear behavior, where the voltage response begins to saturate at higher input powers. As illustrated in Fig. 2.10 (a) and (b), different input combinations (00, 01/10, and 11) correspond to distinct OVC input powers. Based on the nonlinear transfer curve, the resonance shifts for  $\lambda_{01/10}$  and  $\lambda_{11}$  are very close to each other, whereas both are clearly separated from  $\lambda_{00}$ . By appropriately choosing the initial detuning of the microring, the logic function can therefore be defined. In the OR configuration (Fig. 2.10 (a)), the ring is tuned such that  $\lambda_{00} \approx \lambda_{\text{sup}}$ . For the "00" input, the resonance aligns with the supply wavelength and light is dropped, yielding low output power and a logical "0." For any nonzero input (01, 10, or 11), the resonance shifts away, allowing light transmission that corresponds to a logical "1." Conversely, in the NOR configuration (Fig. 2.10 (b)), the ring is initially biased slightly off-resonance. As in the OR case, the phase shifters align the two inputs in phase so that they interfere constructively at the MMI, ensuring the correct combined power is delivered to the OVC. Under this biasing condition, the "00" input yields a logical "1," while all other input combinations shift the resonance toward  $\lambda_{\text{sup}}$  and suppress the output, producing a logical "0."

Additional logic functions such as XOR and XNOR can be implemented by adjusting the input phases with the phase shifters  $V_{C1}$  and  $V_{C2}$ . In this case, destructive interference is enforced at the

MMI combiner, so that the combined power  $P_m$  is nonzero only for the "01" and "10" states, while vanishing for "00" and "11." By selecting the initial biasing of the resonance appropriately, XOR or XNOR behavior can then be achieved.

Figure 2.9: Optical power-to-voltage characterization. Measured OVC output voltage as a function of input optical power ( $P_A$  or  $P_B$ ) for different input logic  $P_{AB}$  configurations: 00, 01, 10, 11.

Figure 2.10: Operational principle of the zero-bias optical logic gate [27]. (a) OR gate implementation and (b) NOR gate implementation.

At a high level, the design allows an optical logic gate to operate without any electrical gain. The main practical challenge, however, lies in controlling the phase of the input signals. The thermopotic phase shifters must be tuned with high precision to ensure that the two inputs arrive at the MMI in the desired phase relation. For OR and NOR gates, the signals must be aligned in phase so that they interfere constructively, whereas for XOR and XNOR, a 180° phase difference must

be enforced to create destructive interference. Any deviation in phase alignment directly alters the combined power at the MMI output, leading to errors in logic functionality and reduced cascadability.

Second, the demonstrated speed is restricted to 10 Mbps [28], primarily due to the slow response of the zero-bias PDs. In photovoltaic mode, the high junction resistance combined with the intrinsic capacitances of the PDs and the MRM produces a large RC time constant on the order of tens to hundreds of nanoseconds. This confines the bandwidth to only a few megahertz. In principle, the OVC could operate in reverse-biased (photoconductive) mode, which would enable drift-dominated transport, reduced resistance, and multi-gigabit per second data rates. However, doing so requires an external electrical supply and an I–V conversion stage, eliminating the self-powered feature that defines the novelty of the zero-bias architecture. Moreover, under reverse bias, the nonlinear power-to-voltage characteristic of the PD stack largely disappears, eliminating the saturating transfer curve that is central to distinguishing between input states. Thus, the speed limitation is not fundamental to photonic integration itself but rather a direct consequence of maintaining zero-bias operation, which simultaneously provides both self-powered functionality and the nonlinear *P–V* response used for logic realization.

### 2.3.2 Optical Logic Gate Realization Using Feedback-Controlled PN-Junction Tuning

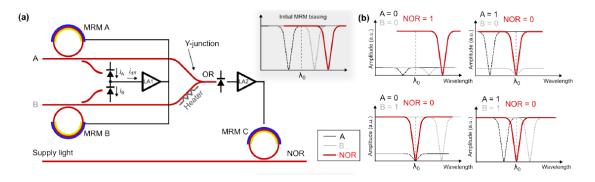

Reference [21] presents a method for implementing universal optical logic gates (UOLGs) based on the electro-optic tuning of silicon MRMs using feedback from photodetected input signals. The core architecture relies on dynamic tuning of MRM resonances through PN-junction tuning. As illustrated in Fig. 2.11(a), two optical inputs, A and B, are coupled into MRMs A and B, whose resonances are initially biased symmetrically around the operating wavelength  $\lambda_0$  (shown in the shaded region of Fig. 2.11(a)). A small portion of the transmitted signals is tapped and converted into photocurrents  $i_A$  and  $i_B$ . The difference current,  $i_{\rm diff}=i_A-i_B$ , is amplified by a limiting amplifier (LA1), and the resulting voltage is fed back to modulate the PN junctions of MRMs A and B, dynamically shifting their resonances to enforce the correct logic state.

If  $i_{\rm diff} > 0$ , meaning input A is logical "1" and input B is logical "0," the applied feedback

shifts the resonances of MRMs A and B toward shorter wavelengths, resulting in a deeper suppression at the output of MRM A. Conversely, if  $i_{\rm diff} < 0$ , corresponding to input A = "0" and input B = "1," the feedback shifts the resonances toward longer wavelengths, enhancing suppression at the output of MRM B. When the inputs are equal (00 or 11), the difference current vanishes and the resonances remain at their initial bias points. This behavior is only possible with careful initial detuning of MRMs A and B around  $\lambda_0$ , ensuring that the feedback response produces the intended logical outputs. As mentioned earlier, the feedback system also enhances suppression at the outputs corresponding to the logical "0" state and sharpens the transition between "0" and "1" levels, improving the overall contrast of the logical levels.

The remaining optical signals from MRMs A and B are then phase-aligned using a thermooptic heater located next to the Y-junction combiner and subsequently combined in the Y-junction,

whose output effectively performs an OR operation. This stage once again highlights the critical

role of phase control. The signals must be aligned in phase so that they interfere constructively

at the combiner. Any phase mismatch would degrade the interference contrast and distort the OR

functionality. As with other interference-based schemes, this reliance on precise phase alignment

represents a practical constraint. Thus, the overall effectiveness of the architecture depends not only

on the feedback-controlled resonance tuning of the MRMs but also on maintaining stable phase

alignment at the Y-junction.

Figure 2.11: PN-junction feedback-based control scheme for implementing optical logic gates using MRMs [20]. (a) Circuit schematic for NOR gate. (b) Operational principle of NOR gate.

To complete the logic function, a third MRM (MRM C) is introduced, which is initially biased slightly off-resonance and supplied with a constant optical input. Its resonance is controlled by the output of the Y-junction after detection and amplification via LA2. When the combined output of the Y-junction corresponds to a logical "0," the resonance of MRM C remains unchanged, allowing the supply light to pass through and producing a logical "1" at the output. Conversely, when the Y-junction output is logical "1," the applied voltage shifts the resonance of MRM C toward shorter wavelengths, bringing it into alignment with the input laser. As a result, the supply light is dropped, and the output of MRM C becomes logical "0." In this way, MRM C functions as an optical inverter, and the combination of the OR output with this inversion yields the NOR function.

In addition to demonstrating NOR logic, the paper also shows that by initially biasing MRMs A and B in an alternative configuration, summing their photocurrents instead of differencing them, and adjusting the thermo-optic heater in one arm of the Y-junction, an optical AND function can be realized. Applying the same inversion stage to this output then yields a NAND gate.

In this work, no physical MRMs were fabricated; instead, a single UOLG was implemented on a programmable mesh of  $2 \times 2$  Mach–Zehnder interferometers (MZIs) configured to emulate MRM behavior. The full SR latch, comprising two cross-coupled gates, was not realized experimentally but only demonstrated through software simulation on a larger photonic mesh. Another important consideration is the logic control circuitry, particularly the limiting amplifiers (LA1 and LA2) that generate the feedback signals. These amplifiers were not realized on-chip or on-board; rather, their behavior was emulated entirely in software. The paper does not provide detailed electrical specifications for these components, such as gain, bandwidth, or noise performance, making it difficult to evaluate the feasibility of a fully integrated hardware implementation.

In summary, Reference [21] presents a promising conceptual framework for scalable optical logic, supporting universal operations and enabling more complex functions such as optical latches. However, accurate phase alignment remains the critical challenge, since the heater before the Y-junction must be finely adjusted to guarantee the inputs combine in the proper phase. In addition, each gate requires three MRMs, all of which must be accurately biased, leading to increased area and higher control complexity if implemented on a photonic circuit.

### 2.3.3 Non-MRM-Based Structures

Beyond MRM-based implementations, several alternative device platforms have been investigated for realizing OLGs. These approaches exploit different physical mechanisms, offering distinct advantages and challenges compared to MRM-based architectures.

### **Quantum-Dot SOA-MZI Based Logic Gates**

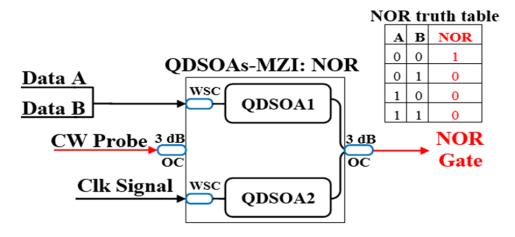

Reference [11] proposed an ultrafast all-optical NOR gate using a MZI with quantum-dot semi-conductor optical amplifiers (QDSOAs). Compared to bulk or quantum-well SOAs, QDSOAs provide shorter carrier relaxation times, higher saturation power, lower noise figure, and improved temperature stability.

As shown in Fig. 2.12, data signals A and B are combined and injected into one QDSOA through a wavelength-selective coupler (WSC), while the clock signal (a constant stream of logical "1") is directed into the other. A CW probe is split by a 3 dB coupler and sent into both arms, with all inputs assigned distinct wavelengths. When the data or clock signals are present, they saturate the QDSOAs, changing the carrier density and refractive index, which shifts the phase of the CW probe.

Figure 2.12: QDSOA–MZI based all-optical NOR gate with corresponding truth table [11].

The MZI is initially biased at destructive interference. For input "00," only the clock arm is saturated, producing a phase imbalance that results in constructive interference and a logical "1" at the output. For inputs "01," "10," or "11," both arms are saturated, so the probe beams remain

phase-aligned and recombine destructively, yielding logical "0." This realizes the NOR operation.

The CW probe is distinguished from the control signals (A, B, Clk) by both power and wavelength. The control beams are launched with higher power to drive QDSOA saturation, while the probe is kept weak so that it only experiences the induced phase shift.

This work was validated through simulation. In practice, implementation would require a phase shifter to accurately bias the interferometer arms, as well as electrical biasing for the two QDSOAs used in each gate. Furthermore, the scheme depends on separate wavelengths for A, B, Clk, and the CW probe, which complicates the system. Overall, this approach demonstrates ultrafast operation and improved carrier dynamics over bulk and quantum-well SOAs, but at the expense of higher device and system complexity.

#### Photonic Crystal Logic Gates Based on the Kerr Effect

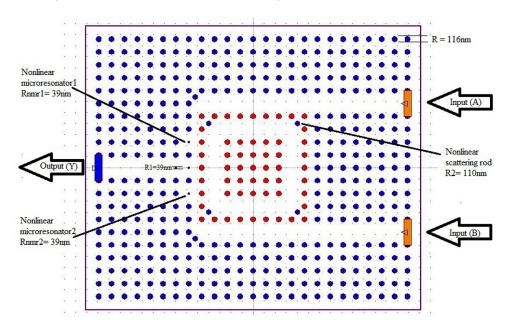

Reference [29] presented an all-optical AND gate based on a two-dimensional photonic crystal (PhC) ring resonator structure exploiting the nonlinear Kerr effect. The device consists of GaAs dielectric rods arranged in air, where the intensity-dependent refractive index variation enables nonlinear switching. The overall structure is shown in Fig. 2.13.

Figure 2.13: Schematic of the Kerr-effect-based photonic crystal AND gate structure [29].

The main element is the central PhC ring resonator (red rods), where the Kerr nonlinearity causes an intensity-dependent index change that shifts the resonance. Inputs A and B are injected through waveguides on the right. With only one input active, the resonance shift is too small for significant transmission, so the output remains low. When both inputs are present, the higher combined intensity produces a sufficient resonance shift, enabling strong transmission at the output port, thus realizing the AND function. Two nonlinear scattering rods (radius 110 nm), together with two auxiliary microresonators (radius 39 nm) near the output waveguide, serve as supporting features that improve coupling efficiency and enhance the output contrast ratio.

This structure achieves a compact footprint and picosecond-scale response. Its main limitations are the relatively high switching power, sensitivity to material nonlinearities, and a lack of optical signal regeneration, which limits large-scale deployment.

### 2.4 Logic control circuit components

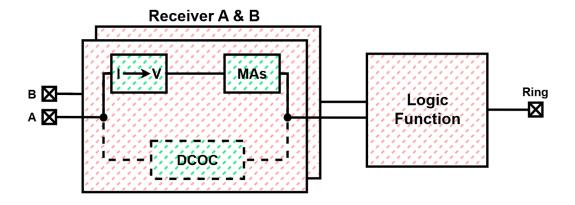

While the previous section discussed two MRM-based optical logic gate implementations, both rely on simplified or emulated logic control schemes. In contrast, the present approach uses a dedicated electrical logic control circuit to interface with photodetected signals and drive the MRMs. These photocurrents are generated by PDs integrated within the PIC. This block typically performs two key functions: (1) it receives the input signals as photocurrents and processes them, acting as an optical receiver, and (2) it generates the electrical signals needed to modulate the MRMs, acting as a modulator driver.

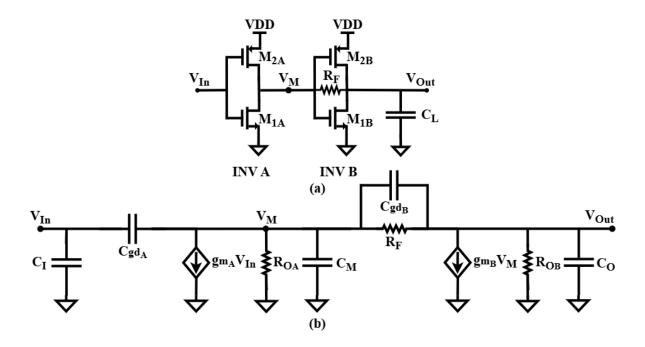

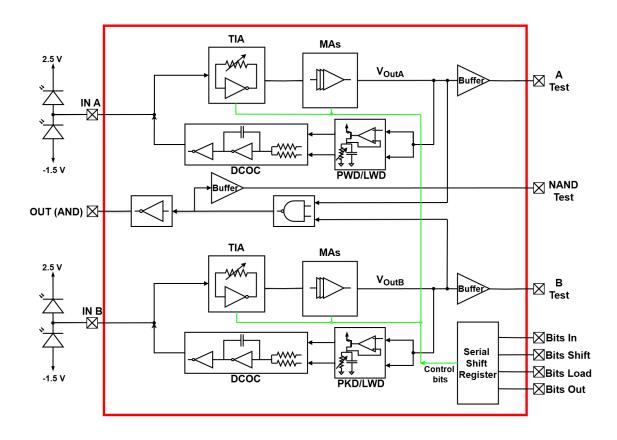

Fig. 2.14 presents a high-level block diagram of the logic control circuit, highlighting three essential building blocks commonly used for optical-to-electrical conversion and signal control: I–V conversion stages, main amplifiers (MAs), and DC offset compensation (DCOC) circuits. To understand the functional requirements of such a circuit, it is helpful to examine these core components, which are described in the following subsections.

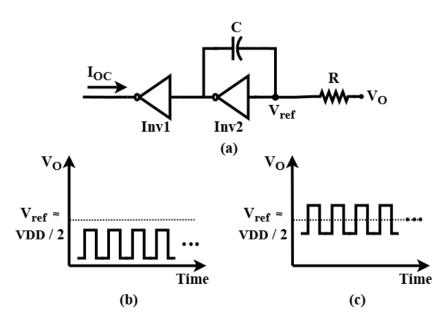

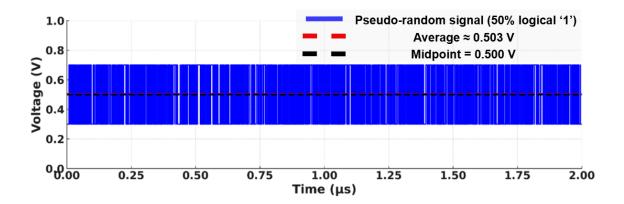

Figure 2.14: Overall block diagram of the logic control circuit, illustrating its key functional components

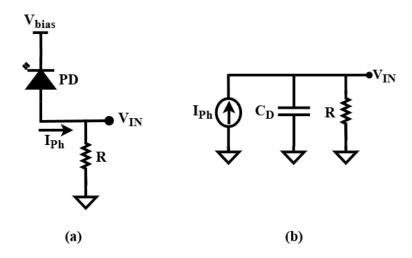

### 2.4.1 I-V Conversion Circuits

In optical logic systems, the photocurrent generated by PDs should be converted into voltage signals for further electronic processing. This conversion is typically performed by an I-V conversion circuit. This circuit is a crucial building block in any optical system. An I-V conversion circuit serves the dual purpose of converting photocurrent to voltage, and amplifying the signal to levels suitable for post-amplification or logic control.

The first and simplest approach for converting photocurrent to voltage in optical front-ends is the use of a resistor [30]. As it is illustrated in Fig. 2.15, the PD is directly connected to a load resistor  $R_C$ , and the voltage is given by:

$$V_{\rm IN} = I_{\rm PD} \times R_C \tag{5}$$

Figure 2.15: Resistor-based I–V conversion: (a) circuit schematic and (b) AC small-signal model.

While this topology offers simplicity, it suffers from a fundamental trade-off between gain and bandwidth. The load resistor, together with the total input capacitance  $C_D$  (including PD junction capacitance and pad parasitics), forms a first-order low-pass filter. The resulting 3-dB bandwidth is given by:

$$f_{3\,\mathrm{dB}} = \frac{1}{2\pi R_C C_D} \tag{6}$$

Combining the two equations shows that increasing  $R_C$  improves voltage gain but simultaneously reduces bandwidth:

$${\rm Gain} = R_C \quad {\rm and} \quad {\rm Bandwidth} \propto \frac{1}{R_C} \eqno(7)$$

This inverse linear relationship between gain and bandwidth limits the suitability of this approach in high-speed optical systems. However, its simplicity makes it attractive in low-speed or proof-of-concept scenarios, or in cases where the total capacitance is very small—such as in monolithic integration where pad capacitance is eliminated.

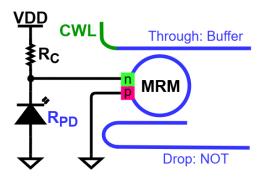

A minimal optical logic gate can also be envisioned by directly connecting a PD, a load resistor, and an MRM, as illustrated in Fig. 2.16. In this system, the photocurrent generated by the PD is converted to a voltage across  $R_C$ , which directly drives the MRM and shifts its resonance. The bandwidth is limited by the RC time constant of the load resistance and the total capacitance at the

node:

$$f_{3dB} = \frac{1}{2\pi R_C \left( C_{PD} + C_{MRM} + C_{pad} \right)}.$$

(8)

Figure 2.16: Minimal OLG using PD, resistor  $R_C$ , and MRM.

Here, both the PD junction capacitance and the intrinsic capacitance of the MRM contribute to the effective load capacitance. If the resistor is implemented on-chip inside the PIC, then the total capacitance is limited to  $C_{PD} + C_{MRM}$ , and the speed can be improved. However, if an off-chip resistor is used, the additional pad capacitance  $C_{pad}$  must be included in the total load, which further reduces the achievable bandwidth and makes the RC trade-off even more restrictive.

The operating voltage across the MRM depends on the input photocurrent  $I_{PD}$ . When the input optical power is high, the current is large, and the node voltage approaches

$$V_{\text{mod,L}} \approx VDD - R_C \times I_{PD,H}$$

(9)

while for low input optical power, the current is small and the node voltage rises toward

$$V_{\text{mod,H}} \approx VDD - R_C \times I_{PD,L} \tag{10}$$

where  $I_{PD,H}$  and  $I_{PD,L}$  represent the photocurrents under high and low input levels, respectively. These two levels determine the effective modulation swing applied to the MRM.

In general, the modulation voltage swing can be expressed as

$$V_{\text{mod}} = I_{\text{PD,p-p}} \times R_C \tag{11}$$

where  $I_{PD,p-p}$  is the peak-to-peak photocurrent corresponding to the optical input. As shown in (9) and (10), the first inversion occurs in the I–V conversion stage, while the second inversion is introduced by the MRM itself due to the negative slope of the resonance curve when the operating point lies on the right side of the resonance (see Fig. 2.7 (b)). To ensure that the modulation swing between these levels is sufficient for proper logic operation, a relatively large  $R_C$  is required. As a result, the through port realizes a buffer function, whereas the drop port provides the complementary NOT function.

In addition, the value of  $R_C$  must also exceed a certain minimum threshold to ensure a minimum optical gain magnitude of unity, i.e.,  $|Gain| \ge 1$ . A detailed explanation and derivation of this condition, along with numerical estimates for the fabricated device, will be presented in Section 3.1.1.

Overall, the appropriate choice of  $R_C$  depends on several design factors, including the input optical signal levels, the amplitude of the desired modulation voltage, the supply voltage VDD, the required optical gain, and the targeted speed of operation.

For example, if we assume an input optical power swing of  $35 \,\mu\text{W}$  (with low and high levels of  $5 \,\mu\text{W}$  and  $35 \,\mu\text{W}$ , respectively), the corresponding photocurrent swing is  $I_{\text{PD,p-p}} = 28 \,\mu\text{A}$  ( $I_{PD,L} = 4 \,\mu\text{A}$ ,  $I_{PD,H} = 32 \,\mu\text{A}$ ). With a supply voltage of  $V_{DD} = 5 \,\text{V}$ , and assuming a desired modulation amplitude of approximately  $4 \,\text{V}$ , the required resistance is  $R_C = 4/(28 \times 10^{-6}) \approx 143 \,\text{k}\Omega$ . Under these conditions, the modulation levels are approximately  $V_{\text{mod,L}} \approx 0.4 \,\text{V}$  and  $V_{\text{mod,H}} \approx 4.4 \,\text{V}$ , providing the desired  $4 \,\text{V}$  swing.

To evaluate the bandwidth, we use (8). With capacitances of  $C_{MRM}=30~\mathrm{fF}$  and  $C_{PD}=30~\mathrm{fF}$ , the total capacitance for the on-chip case is  $C_{\mathrm{on\text{-}chip}}=60~\mathrm{fF}$ , which yields a 3-dB frequency of  $f_{\mathrm{3dB,on\text{-}chip}}\approx18.6~\mathrm{MHz}$ . If the resistor is implemented off-chip, the additional pad capacitance of  $C_{pad}\approx150~\mathrm{fF}$  increases the total capacitance to  $C_{\mathrm{off\text{-}chip}}\approx210~\mathrm{fF}$ , resulting in lower bandwidth of  $f_{\mathrm{3dB,off\text{-}chip}}\approx5.3~\mathrm{MHz}$ .

This PD-resistor-MRM configuration represents an extremely simple architecture, and demonstrates the feasibility of a nearly all-optical logic gate. However, the severe speed limitation due to

the RC trade-off, limited modulation swing, and strong dependence on optical input levels are the main challenges of this structure.

Returning to I–V conversion structures, the gain–bandwidth trade-off inherent in resistor-based implementations can be mitigated by employing transimpedance amplifiers (TIAs) in high-speed optical systems. One approach is to incorporate active feedback, which lowers the input impedance seen by the PD, thereby minimizing RC delay and avoiding the bandwidth limitations imposed by the PD's parasitic capacitance. This enables high transimpedance gain and wide bandwidth, making TIAs well-suited for fast and energy-efficient signal processing.

Among various TIA implementations, inverter-based architectures are particularly attractive in modern CMOS optical receivers. These designs leverage high-gain CMOS inverters, offering high transconductance, rail-to-rail output swing, and excellent compatibility with low-voltage operation in a compact form factor [30]. As a result, inverter-based shunt-feedback TIAs have become a popular choice for high-speed, low-power front-ends, providing an efficient interface between the PD and subsequent circuits in optical receivers.

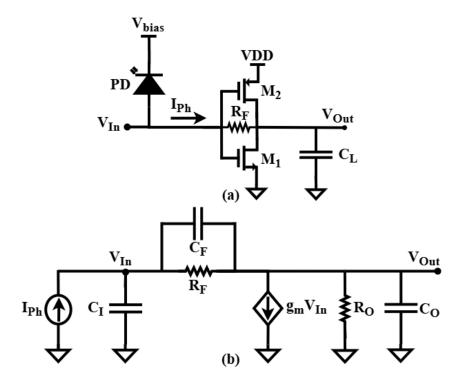

The schematic of a CMOS inverter-based shunt feedback TIA is shown in Fig. 2.17 (a). When  $I_{\rm in}=0$ , the input and output voltages of the inverter are equal, i.e.,  $V_{\rm In}=V_{\rm Out}$ . This defines the operating point of the TIA in an inverter-based shunt-feedback configuration. To analyze the frequency response of the TIA, its AC small-signal model, shown in Fig. 2.17 (b), is considered. This model captures the dominant parasitic capacitances and resistances, enabling analytical evaluation of the amplifier's frequency-dependent behavior. The circuit parameters are defined as follows:

$$g_m = g_{m1} + g_{m2} (12)$$

$$R_0 = r_{o1} \parallel r_{o2} \tag{13}$$

$$C_I = C_{gs1} + C_{gs2} + C_D (14)$$

$$C_O = C_{\text{db1}} + C_{\text{db2}} + C_L \tag{15}$$

$$C_F = C_{\text{gd1}} + C_{\text{gd2}} \tag{16}$$

Figure 2.17: CMOS inverter-based TIA: (a) circuit schematic and (b) small-signal model.

The transfer function from the input current of the small signal  $I_{IN}$  to the output voltage  $V_{Out}$  is expressed as [31]:

$$\frac{V_o}{I_{\rm in}} = \frac{(R_F C_F s + 1 - g_m R_F) R_O}{R_F R_O C s^2 + [R_F (1 + g_m R_O) C_F + (R_F + R_O) C_I + R_O C_O] s + 1 + g_m R_o}$$

(17)

where  $C = C_I C_O + C_I C_F + C_O C_F$ .

Assuming  $C_F$  is smaller than the other parasitic capacitances and contributes minimally to the frequency response, the expression simplifies to:

$$\frac{V_{Out}}{I_{In}} = \frac{(1 - g_m R_F) R_O}{R_F R_O C_I C_O s^2 + [(R_F + R_O) C_I + R_O C_O] s + 1 + g_m R_O}$$

(18)

At low frequencies, the gain can be approximated by: